# SUZAKU-V ハードウェアマニュアル

Version 1.0.1

SZ410-U00

株式会社アットマークテクノ

http://www.atmark-techno.com/

SUZAKU 公式サイト

http://suzaku.atmark-techno.com/

# 目次

| 1. は         | じめに   |                                                                                    | 1  |

|--------------|-------|------------------------------------------------------------------------------------|----|

| 2. 注         | 意事項   | 頁                                                                                  | 2  |

| 2.1.         |       | -<br>全に関する注意事項 ······                                                              |    |

| 2.2.         | 保証    | 正に関する注意事項 ····································                                     | 2  |

| 2.3.         | 取り    | )扱い上の注意事項                                                                          | 3  |

| 2.4.         | FP(   | GA 使用に関しての注意事項 ····································                                | 4  |

| 2.5.         | ソフ    | トウェア使用に関しての注意事項・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                | 4  |

| 3. 作         | 業の前   | 前に ····································                                            | 5  |

| 3.1.         |       | <b>帯するもの</b>                                                                       |    |

| 4. 概         |       |                                                                                    |    |

| 4.1.         | SZ4   | 410-U00 の特徴 ······                                                                 | 6  |

| 4.2.         |       | <b>羕</b> ·······                                                                   |    |

| 4.3.         |       | 本ブロック図 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                        |    |

| 4.4.         | 機能    | 년                                                                                  |    |

| 4.           | 4.1.  | プロセッサ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          | -  |

| 4.           | 4.2.  | バス                                                                                 | ·  |

| 4.           | 4.3.  | メモリ                                                                                |    |

| 4.           | 4.4.  | 割り込み                                                                               |    |

| 4.           | 4.5.  | タイマ                                                                                |    |

| 4.           | 4.6.  | シリアルコンソール                                                                          |    |

| 4.           | 4.7.  | LAN                                                                                | 12 |

| 4.           | 4.8.  | 外部 I/O ·····                                                                       |    |

| 4.           | 4.9.  | FPGA コンフィギュレーション ·····                                                             |    |

| 4.           | 4.10. | ソフトウェアリセット機能                                                                       | _  |

|              | 4.11. | JTAG····                                                                           |    |

|              | 4.12. | 設定用ジャンパ                                                                            | _  |

|              | 4.13. | LED                                                                                |    |

|              | 4.14. | 電源入力+3.3V                                                                          |    |

|              | 4.15. | 内部ロジック用電源出力+3.3V ·······                                                           |    |

|              | 4.16. | 内部電源シーケンス                                                                          |    |

|              |       | ップ ····································                                            |    |

| 5.1.         |       |                                                                                    |    |

|              |       | プンアサイン・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          |    |

|              |       | 'ターフェース仕様 ·····・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                    |    |

| 7.1.         |       | #インターフェースの配直                                                                       |    |

| 7.2.<br>7.3. |       | N1 RS-232C ···································                                     |    |

| 7.3. $7.4.$  |       | N3 外部 I/O コネクタ ····································                                |    |

| 7.5.         |       | N4 外部 I/O コネクタ ····································                                |    |

| 7.6.         |       | N5 外部 I/O コネクタ ····································                                |    |

| 7.7.         |       | N6 電源入力+3.3V コネクタ ····································                             |    |

| 7.8.         |       | N7 FPGA 用 JTAG コネクタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                            |    |

| 7.9.         |       | N7 F1 GA 州 8 IAG ニネック<br>N8 CPLD 用 JTAG コネクタ · · · · · · · · · · · · · · · · · · · |    |

| 7.3.         |       | No CI LD 用 3 IAG ユネクタ<br>D1,D3 LED                                                 |    |

| 7.10         |       | /1,D9 HED<br>P1,JP2 設定用ジャンパ ····································                   |    |

| 7.12         |       | SUZAKU L2 Ethernet 10/100BASE-T ······                                             |    |

|              | 板形岩   |                                                                                    |    |

### 表目次

|          |        | SZ410-U00 仕様 ·····                                                |    |

|----------|--------|-------------------------------------------------------------------|----|

| ā        | 長 5-1  | SZ410-U00 メモリマップ                                                  | 18 |

|          |        | FPGA ピンアサイン 外部 I/O 関連(1/3) ····································   |    |

|          |        | FPGA ピンアサイン 外部 I/O 関連(2/3) ····································   |    |

| <u> </u> | 長 6-3  | FPGA ピンアサイン 外部 I/O 関連(3/3) ···································    | 21 |

|          |        | FPGA ピンアサイン 内部デバイス関連(1/4) ····································    |    |

|          |        | FPGA ピンアサイン 内部デバイス関連(2/4) ····································    |    |

|          |        | FPGA ピンアサイン 内部デバイス関連(3/4) ····································    |    |

|          |        | FPGA ピンアサイン 内部デバイス関連(4/4) ···································     |    |

| 3        | 長 6-8  | FPGA ピンアサイン JTAG、コンフィギュレーション関連 ······                             | 26 |

|          |        | 各種インターフェースの内容                                                     |    |

|          |        | シリアルコンソールの設定                                                      |    |

|          |        | CON1 RS-232C ····                                                 |    |

|          |        | CON2 外部 I/O、SPI フラッシュ用 SPI コネクタ ······                            |    |

|          |        | CON3 外部 I/O コネクタ ······                                           |    |

|          |        | CON4 外部 I/O コネクタ ····································             |    |

|          |        | CON5 外部 I/O コネクタ ······                                           |    |

|          |        | CON7 Virtex-4 FX 用 FPGA JTAG コネクタ ······                          |    |

| 3        | 長 7-9  | CON8 Virtex-4 FX 用 CPLD JTAG コネクタ ······                          | 32 |

|          |        | 0 D1, D3 LED                                                      |    |

|          |        | 1 JP1、JP2 設定用ジャンパ ····································            |    |

| 3        | 長 7-12 | 2 L2 Ethernet 10/100 BASE-T · · · · · · · · · · · · · · · · · · · | 33 |

|          |        |                                                                   |    |

| 図目》      | 欠      |                                                                   |    |

|          |        |                                                                   | _  |

| _        |        | SZ410-U00 ブロック図 · · · · · · · · · · · · · · · · · · ·             |    |

| _        |        | SZ410-U00 バス構成 ·····                                              |    |

| _        |        | FPGA コンフィギュレーション                                                  |    |

|          |        | CoreConnect のビットラベルと信号名                                           |    |

|          |        | 各種インターフェースの配置                                                     |    |

| 3        | ⊻ 8-1  | SZ410-U00 の基板形状 ······                                            | 34 |

# 1.はじめに

このたびは SUZAKU-V(SZ410-U00)をお求めいただき、ありがとうございます。

本マニュアルには SUZAKU-V(SZ410-U00)のハードウェアの仕様や使用方法について記載しております。 SUZAKU-V(SZ410-U00)の機能を最大限引き出すために、ご活用いただければ幸いです。

# 2.注意事項

## 2.1.安全に関する注意事項

SZ410-U00 を安全にご使用いただくために、特に以下の点にご注意くださいますようお願いいたします。

本製品には一般電子機器用(OA機器・通信機器・計測機器・工作機械等)に製造された半導体部品を使用していますので、その誤作動や故障が直接生命を脅かしたり、身体・財産等に危害を及ぼす恐れのある装置(医療機器・交通機器・燃焼制御・安全装置等)に組み込んで使用したりしないでください。また、半導体部品を使用した製品は、外来ノイズやサージにより誤作動したり故障したりする可能性があります。ご使用になる場合は万一誤作動、故障した場合においても生命・身体・財産等が侵害されることのないよう、装置としての安全設計(リミットスイッチやヒューズ・ブレーカ等の保護回路の設置、装置の多重化等)に万全を期されますようお願い申しあげます。発熱により高温になる部品があります。周囲温度や取り扱いによってはやけどの恐れがあります。電源が入っている状態および電源切断後しばらくは本製品に触れないようお願い申しあげます。

## 2.2. 保証に関する注意事項

#### ● 製品保証範囲について

付属品(ソフトウェアを含みます)を使用し、取扱説明書、各注意事項に基づく正常なご使用に限り有効です。 万一正常なご使用のもと製品が故障した場合は、初期不良保証期間内であれば新品交換をさせていただきま す。

#### ● 保証対象外になる場合

次のような場合の故障・損傷は、保証期間内であっても保証対象外になります。

- 1. 取扱説明書記載の使用方法、または注意に反したお取り扱いによる場合

- 2. 改造・調整や部品交換による場合。または正規のものを使用していないか、あるいは過去に使用されていた場合

- 3. お客様のお手元に渡った後の輸送、移動時の落下等お取り扱いの不備による場合

- 4. 火災・地震・水害・落雷・その他の天災、公害や異常電圧による場合

- 5. AC アダプタ・ケーブル等の付属品について、同梱のものを使用していない場合

- 6. 付属品がすべて揃っていない場合

#### ● 免責事項

弊社に故意または重大な過失があった場合を除き、製品の使用および、故障、修理によって発生するいかなる 損害についても、一切の責任を負わないものとします。

本製品は購入時の初期不良以外の保証を行っておりません。保証期間は商品到着後2週間です。本製品をご購入しましたらお手数でも必ず動作確認を行ってからご使用ください。本製品に対して注意事項を守らずに発生した故障につきましては保証対象外となります。

## 2.3.取り扱い上の注意事項

劣化、破損、誤動作、発煙、発火の原因となることがあります。取り扱い時には以下のような点にご注意ください。

## **八**入力電源

3.3V+3%以上の電圧を入力しないでください。また、極性を間違わないでください。

### *↑* インターフェース

各インターフェース(外部 I/O、RS-232C、Ethernet、JTAG)には規定以外の信号を接続しないでください。また、信号の極性、入出力方向を間違わないでください。

## / 本製品の改造

本製品について、外部 I/O コネクタ及び JTAG コネクタ(CON2、CON3、CON4、CON5、CON7)へのコネクタの増設以外の改造を行った場合は保証対象外となりますので、十分にご注意ください。

コネクタを増設する際にはマスキングを行い、周囲の部品に半田くず、半田ボール等付着しない様十分にご注意ください。

なお、改造を行う場合は、改造前の動作確認を必ず行うようお願いします。

## **⚠ FPGA** プログラム

周辺回路(ボード上の部品も含む)と信号の衝突(同じ信号に2つのデバイスから出力する)を起こすようなFPGA プログラムを行わないでください。また、FPGA のプログラムを間違わないでください。

## ⚠ 電源の投入

本ボードや周辺回路に電源が入っている状態では絶対に FPGA I/O、JTAG 用コネクタの着脱を行わないでください。

## **介 静電気**

本ボードには CMOS デバイスを使用していますので、ご使用になるまでは帯電防止対策のされている出荷時のパッケージ等にて保管してください。

## *^*√ラッチアップ

電源および入出力ラインからの過大なノイズやサージ、電源電圧の急激な変動等で、使用している CMOS デバイスがラッチアップを起こす可能性があります。一旦ラッチアップ状態になりますと、電源を切断しないかぎりこの状態が維持されるため、デバイスの破損につながることがあります。ノイズの影響を受けやすい入出力ラインには保護回路を導入する、ノイズ源となる装置と共通の電源を使用しない等の対策をとることをお勧めします。

## ⚠衝撃、振動

落下や衝突などの強い衝撃を与えたり、強い振動や遠心力を与えないでください。また、振動部、回転部など への搭載はしないでください。

## ⚠ 高温低温、多湿

極度に高温や低温になる環境や湿度が高い環境で使用しないでください。

## **/ 上塵埃**

塵埃の多い環境では使用しないでください。

## 2.4. FPGA 使用に関しての注意事項

● 本製品に含まれる FPGA プロジェクトについて

本製品に含まれる FPGA プロジェクト(付属のドキュメント等も含みます)は、現状のまま(AS IS)提供されるものであり、特定の目的に適合することや、その信頼性、正確性を保証するものではありません。また、本製品の使用による結果についてもなんら保証するものではありません。

本製品は、ベンダのツール(Xilinx 製 EDK、ISE やその他ベンダツール)やベンダの IP コアを利用し、FPGA プロジェクトの構築、コンパイル、コンフィギュレーションデータの生成を行っておりますが、これらツールに関しての販売、サポート、保証等は行っておりません。

## 2.5. ソフトウェア使用に関しての注意事項

本製品に含まれるソフトウェアについて

本製品に含まれるソフトウェア(付属のドキュメント等も含みます)は、現状のまま(AS IS)提供されるものであり、特定の目的に適合することや、その信頼性、正確性を保証するものではありません。また、本製品の使用による結果についてもなんら保証するものではありません。

# 3.作業の前に

## 3.1. 準備するもの

SZ410-U00 をご使用になる前に、次のものを準備してください。

#### ● 作業用 PC

ハードウェア開発用として Windows XP が動作し、シリアルポート(1 ポート)及びパラレルポート(1 ポート)を持つ PC を準備してください。

ソフトウェア開発用として Linux が動作し、シリアルポート(1 ポート)を持つ PC を準備してください。

#### ● D-Sub9 ピンクロスケーブル

D-Sub9ピン(メスーメス)のクロスケーブルを準備してください。

#### ● D-Sub9 ピン-10 ピン変換ケーブル

D-Sub9 ピンと本ボードのピンヘッダ(10 ピン)を接続するための D-Sub9 ピン-10 ピン変換ケーブルを準備してください。

#### 各種マニュアル及びソースコード

SZ410-U00 に関する各種マニュアルやソースコードを準備してください。これらは開発キット付属 CD-ROM(以降付属 CD-ROM)に収録されています。また、SUZAKU 公式サイトのダウンロードページからダウンロードすることもできます。(http://suzaku.atmark-techno.com/downloads/all)

#### シリアル通信用ソフト

minicom や Tera Term などのシリアル通信用ソフトを準備してください。

#### ● DC3.3V 電源

DC3.3V 出力の電源を準備してください。

#### Xilinx ISE

Xilinx ISE を準備し、インストールしてください。インストール後ソフトウェアアップデートをしてください。\*

#### Xilinx EDK

Xilinx EDK を準備し、インストールしてください。インストール後ソフトウェアアップデートをしてください。\*

#### ● Xilinx Parallel CableⅢ、IVまたはそれ相当品

Parallel CableⅢ、IVまたはそれ相当品を準備してください。\*

<sup>\*</sup> Xilinx 製品の詳細については、Xilinx のホームページ(http://www.xilinx.co.jp/)をご覧になられるか、Xilinx 代理店にお問い合わせください。

# 4.概要

## 4.1.SZ410-U00 の特徴

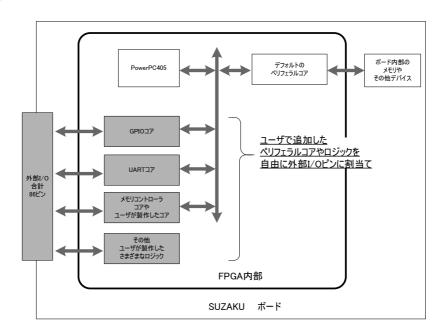

SUZAKU(朱雀)は Xilinx の FPGA をベースとしたボードコンピュータです。

FPGA 上にハードコアプロセッサ PowerPC405 と周辺ペリフェラルコアを構成し、オペレーティングシステムとして Linux を採用しています。 SZ410-U00 は Xilinx の FPGA の中でも、Virtex-4 FX を採用しています。

#### ハードプロセッサと周辺ペリフェラルコアの構築

PowerPC405 や周辺ペリフェラルコアの構築には Xilinx EDK(Embedded Development Kit)を使用します。 EDK は GUI 環境下で PowerPC405 や周辺ペリフェラルコアの各種設定を行い、その設定情報から自動的にネットリストを生成するツールです。

#### カスタマイズ

FPGA の中は、ユーザによってカスタマイズが可能です。また、基板外周にユーザが自由に使える外部 I/O を86 ピン実装しております。例えば、PIO や UART の数を増やし、外部 I/O ピンに割当てるなどのカスタマイズが簡単に行えます。\*

#### LAN

LAN コントローラ(10BASE-T/100BASE-TX)を実装しています。 市販の LAN ケーブル(UTP)が接続できます。

#### オペレーティングシステム

Linux を標準のオペレーティングシステムとして採用していますので、アプリケーションソフトウェアの開発には GNU のアセンブラやCコンパイラ等を使用することができます。

また、LAN コントローラデバイスドライバ、各種プロトコルが最初から用意されていますので、簡単にネットワークに接続できます。

オペレーティングシステムの詳細については、『SUZAKU ソフトウェアマニュアル』を参照ください。

<sup>\*</sup> FPGA のカスタマイズには Xilinx EDK、ISE が必要です。Xilinx 製品の詳細については、Xilinx のホームページ(http://www.xilinx.co.jp/)をご覧になられるか、Xilinx 代理店にお問い合わせください。

# 4.2.仕様

本ボードの主な仕様を以下に示します。

表 4-1 SZ410-U00 仕様

| FPGA   |           | Xilinx Virtex-4 FX XC4VFX12 SF363 |  |  |  |

|--------|-----------|-----------------------------------|--|--|--|

| プロセッサ  |           | PowerPC405(ハードコア)                 |  |  |  |

| 水晶発    | 振器周波数     | 100MHz(FPGA の内部 DCM により逓倍して使用)    |  |  |  |

| メモリ    | BRAM      | 648Kbits                          |  |  |  |

|        | DRAM      | DDR2 SDRAM 32MByte $\times$ 2     |  |  |  |

|        | SPI フラッシュ | 8MByte                            |  |  |  |

| コンフィ   | ゲュレーション   | SPI フラッシュメモリ上に記憶                  |  |  |  |

| JTAG   |           | 1ポート(FPGA用)                       |  |  |  |

| SPI 7  | ラッシュ書込み   | 専用ピン                              |  |  |  |

| Etherr | net       | 10BASE-T/100BASE-TX               |  |  |  |

| シリアハ   |           | UART 115.2kbps                    |  |  |  |

| タイマ    |           | PowerPC 内蔵タイマ                     |  |  |  |

| フリーL   | /0 ピン     | 86ピン                              |  |  |  |

| リセット   | 機能        | ソフトウェアリセット                        |  |  |  |

| 電源     |           | 電圧:3.3V±3%                        |  |  |  |

|        |           | 消費電力:3W typ.(プロセッサ動作時)            |  |  |  |

| 使用温    | 度範囲       | 0°C~60°C                          |  |  |  |

| 基板サ    | イズ        | 72×47mm                           |  |  |  |

# 4.3.全体ブロック図

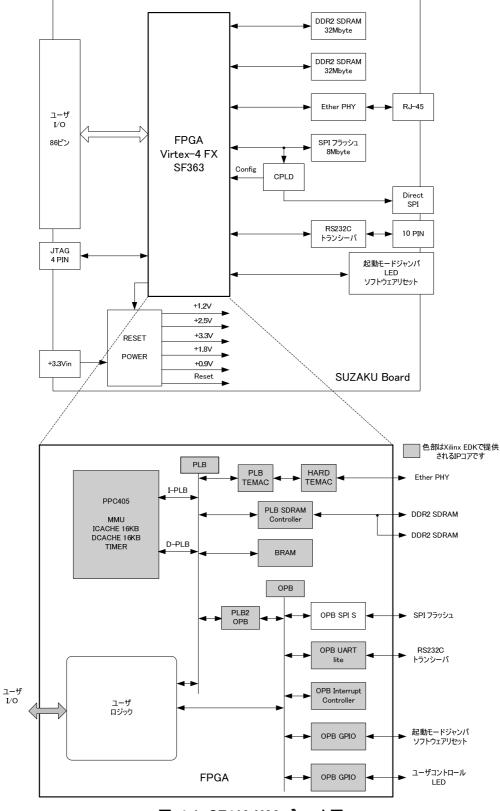

SZ410-U00 の全体ブロック図を以下に示します。

図 4-1 SZ410-U00 ブロック図

## 4.4.機能

#### 4.4.1. プロセッサ

FPGA 内部で PowerPC405 を使用しています。PowerPC405 の概要を以下に示します。

- •32 ビット RISC プロセッサ

- ・32 ビット固定長命令

- ・32 個の汎用 32bit レジスタ

- ·MMU

- ・命令キャッシュ(16KByte, 2-way)とデータキャッシュ(16KByte, 2-way)

#### 4.4.2. バス

- 2種類のバスで構成しています。

- •FPGA 内部 PLB

PowerPC405 と BRAM、PLB DDR2 Controller、PLB TEMAC などのペリフェラル IP コアを接続するバス

·FPGA 内部 OPB

OPB UART lite、OPB INTC などのペリフェラル IP コアを接続するバス

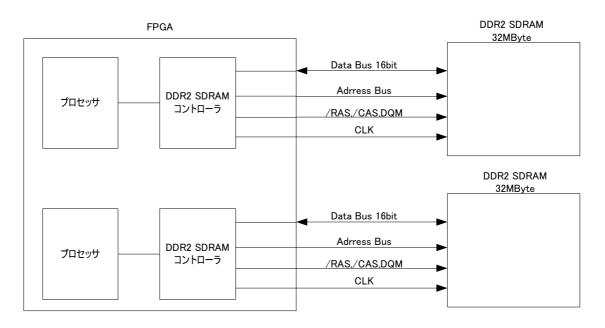

図 4-2 SZ410-U00 バス構成

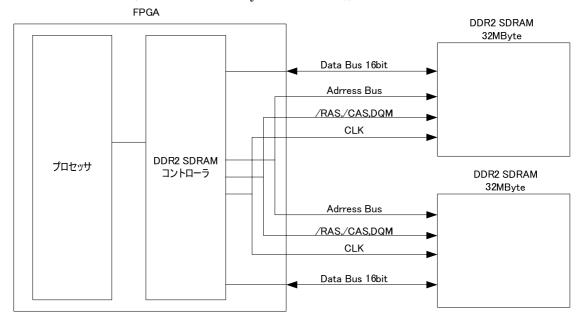

#### 4.4.3. メモリ

- 3種類のメモリで構成しています。

- ・FPGA 内部 BRAM (デフォルト 16KByte) ブートプログラム用として使用しています。起動完了後は、ユーザプログラムで使用することもできます。

- ・FPGA 外部 SPI フラッシュメモリ

8MByte を実装しています。 ブートローダ Hermit や Linux イメージ、FPGA コンフィグデータなどのデータ保存に使用しています。

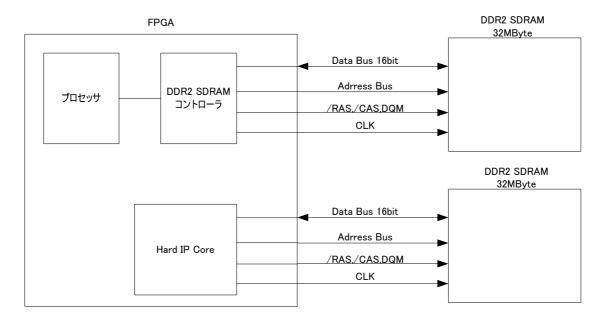

·FPGA 外部 DDR2 SDRAM 32MByte

Linux のメインメモリとして使用しています。 2 枚の DDR2 SDRAM の信号線は、完全に 2 つに分離して FPGA と接続されていますので、 FPGA のプログラムによっては以下のような使い方ができます。

● SUZAKU のデフォルト 単プロセッサ 64MByte Data32bit 幅での使用

● プロセッサ 32MByte Data16bit 幅 + プロセッサ 32MByte Data16bit 幅での使用

● プロセッサ 32MByte Data16bit 幅 + Hard IP Core での使用

#### 4.4.4. 割り込み

OS 用割り込みコントローラに、FPGA 内部で OPB INTC を使用しています。

#### 4.4.5. タイマ

PowerPC405 内のタイマを使用しています。

#### 4.4.6. シリアルコンソール

OS 用シリアルコンソールに FPGA 内部で OPB UART lite を使用しています。OPB UART lite は RS-232Cトランシーバを介し、コネクタ(CON1)に接続しています。RS-232Cトランシーバは、4 チャンネルタイプのものを使用しており、このうち 2 チャンネルを OS 用シリアルコンソールで使用し、残り 2 チャンネルは未使用となっています。これらの未使用の信号に GPIO やユーザロジックを接続してフロー制御をしたり、別の OPB UART lite を接続して 2 ポート目の UART とすることも可能です。

・シリアルコンソールの設定

転送レート 115.2kbps データ 8bit

ストップ bit 1bit フロー制御 なし

#### 4.4.7. LAN

Virtex-4 FX 内蔵の TEMAC (Tri-Mode Ether MAC) と 10BASE-T/100BASE-TX の Ether PHY (SMSC 製)を使用しています。 RJ-45 コネクタを実装しており、 市販の LAN ケーブル (UTP) が接続できます。

#### 4.4.8. 外部 I/O

ユーザが自由に使用できる外部 I/O を 86 ピン実装しています(CON2、CON3、CON4、CON5)。 (コネクタは実装されていません)

外部 I/O は、全て FPGA のフリーI/O ピンと直接接続しています。

FPGAのI/O用電源(VCCO)は、全て内部ロジック用電源+3.3Vから供給しています。

I/O 電圧や駆動電流などの規定値については、Virtex-4 FX のデータシートをご参照ください。

内部ロジック用電源+3.3V は、シーケンス回路及びディレー回路により立ち上がりに最大 20msec の時間がかかります。よって外部 I/O と接続するデバイスは、ラッチアップ等を起こさないために、本ボードの内部ロジック用電源+3.3V 出力を使用するかバッファデバイス等が必要になります。

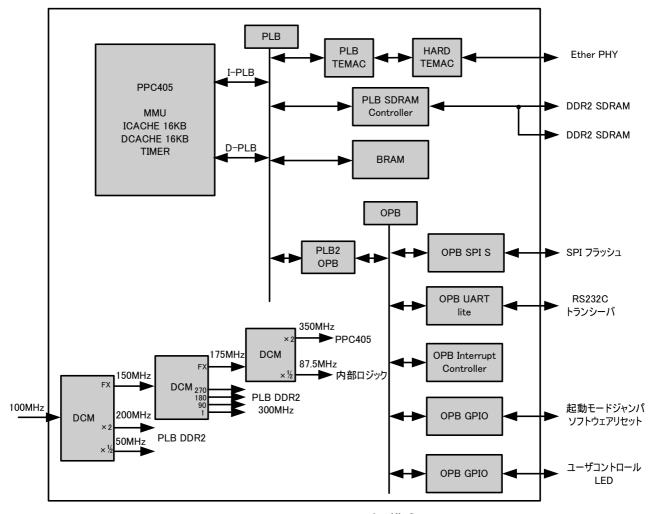

#### 4.4.9. FPGA コンフィギュレーション

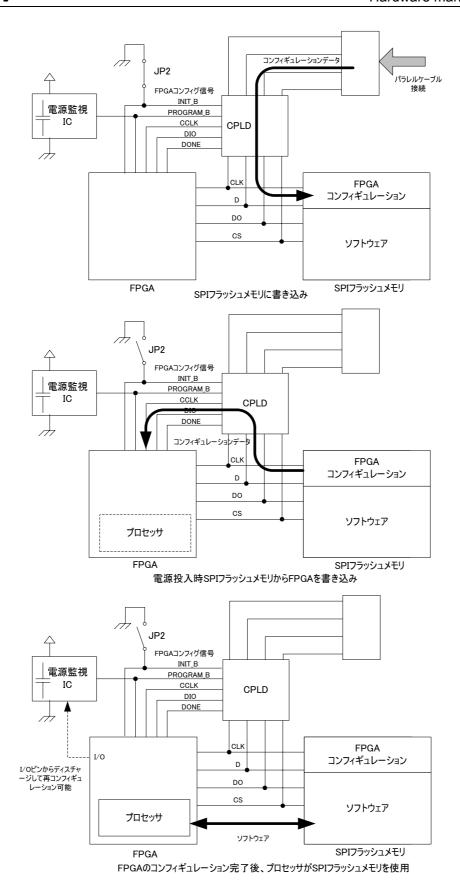

CPLD を使用した SPI コンフィギュレーションを採用しています。

SPI フラッシュメモリは、M25P64(ST マイクロエレクトロニクス製)を使用しています。

SPI フラッシュメモリの書換えには、弊社提供の SPI Writer をご使用ください。 SPI Writer は SPI フラッシュメモリの先頭から 1MByte まで消去し、コンフィギュレーションデータを書き込む SUZAKU の SPI フラッシュメモリ専用の書き込みツールです。"図 4-3 FPGA コンフィギュレーション"にSPIフラッシュメモリに書き込むところから動作するまでの流れを示します。

SUZAKU は SPI フラッシュメモリにソフトウェアのデータやその他データを保存しており、これらのデータを壊さないために専用ツールで書き込みます。

SPI フラッシュメモリの書き込みツールとしては iMPACT の DirectSPI もあります。ただし、DirectSPI は SPI フラッシュメモリのデータを全消去して、コンフィギュレーションデータを書き込むツールであるため、SUZAKU の SPI フラッシュメモリに書き込む際には注意が必要となります。

SPI\_Writer.exe のインストール方法や使い方については、付属 CD-ROM の "¥suzaku¥tools¥spi\_writer-yyyymmdd.zip"(yyyymmdd:更新日)をご参照ください。

図 4-3 FPGA コンフィギュレーション

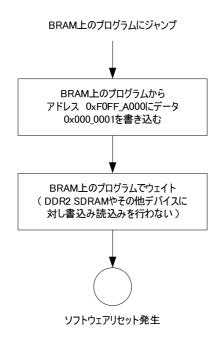

#### 4.4.10. ソフトウェアリセット機能

ソフトウェアリセットを実行すると、フラッシュメモリからコンフィギュレーションデータの再読み込みが行われ、FPGAのコンフィギュレーションが実行され、各デバイス IC へリセットが出力されます。

ソフトウェアリセットは、Linuxの reboot コマンドを使用するか、BRAM 上のプログラムから、直接アドレス 0xF0FF\_A000 にデータ 0x0000\_0001 を書き込むことにより実行できます。BRAM 上のプログラムから直接ソフトウェアリセットを実行する場合は、DDR2 SDRAM やその他デバイスに対し書込み読込み(プログラムの実行を含む)を行わないでください。

BRAM上のプログラムから直接ソフトウェアリセットを実行する場合

#### 4.4.11. JTAG

CON7 は FPGA 用 JTAG コネクタで(コネクタは実装されていません)FPGA の JTAG ピンと直接接続されていま す。 本 JTAG の I/O 電圧は+3.3V ですので、+3.3V に対応した JTAG ケーブルをご使用ください。 TMS、TDI、 TCK は、本ボード内で 4.7k $\Omega$ を介し+3.3V にプルアップされています。

#### 4.4.12. 設定用ジャンパ

設定用ジャンパには、以下の2種類があります。

・起動モードジャンパ (JP1, Virtex-4 FXの W4と接続しています)

起動モードを切り替えるジャンパです。

オープンでオートブートします。

ショートでブートローダモードになります。

(起動モードについての詳細は『SUZAKU ソフトウェアマニュアル』を参照してください)

・FPGA プログラム用ジャンパ(JP2, Virtex-4 FXの E12 INIT Bと接続しています)

SPIフラッシュメモリにプログラムする時に使用するジャンパです。

オープンでノーマルブートします。

(電源再投入時、本ジャンパをショートすると、FPGA に対しコンフィギュレーションを停止させることができ、 その時に SPI フラッシュメモリにプログラムすることができます)

#### 4.4.13. LED

LED には、以下の2種類があります。

・パワーオン LED 緑 (D3)

本ボードに 3.3V が供給されると点灯します。

・ユーザコントロール LED 赤 (D1)

Virtex-4 FX の T4 と接続しています。

SUZAKU のデフォルトの FPGA プロジェクトでは、アドレス 0xF0FF\_A200 にデータ 0x0000\_0000 を書き込むことにより点灯させることができます。

### 4.4.14. 電源入力+3.3V

CON2、CON3 及び CON6 の電源入力+3.3V から本ボードへの電源供給が可能です。 +3.3V は、精度±3%で単調増加とし、極度に短い間隔でのオン/オフ繰り返しは行わないようにしてください。 入力には積層セラミックコンデンサ  $22 \, \mu \, F \times 3$  を実装しています。

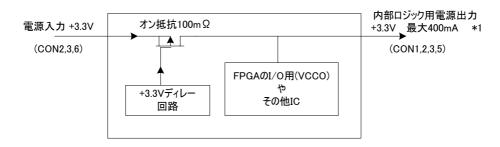

#### 4.4.15. 内部ロジック用電源出力+3.3V

内部ロジック用電源+3.3V は、FPGA の I/O(VCCO)やその他 IC に供給している電源です。 CON1、CON2、CON3、CON5 から、外部のデバイスに合計最大 400mA \*1 の電源供給が可能です。 外部のデバイスの負荷変動が大きい場合、電源入力+3.3V の応答によっては、電圧変動が発生すること があります。

\*1 外部 I/O から信号を出力する場合は、 合計最大電流 = 400mA-外部 I/O 信号の出力電流 となります。

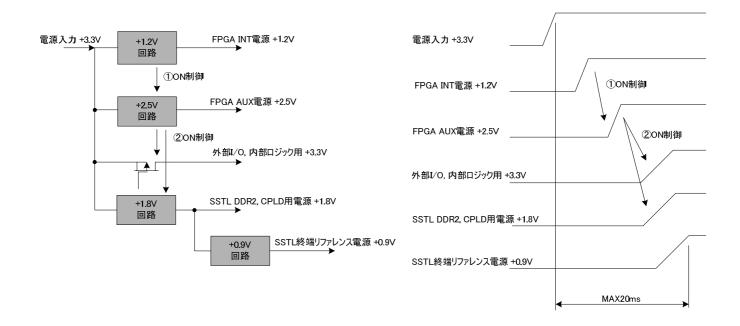

### 4.4.16. 内部電源シーケンス

内部電源は、以下のようなシーケンスで立ち上がります。

# 5.メモリマップ

## 5.1.SZ410-U00 メモリマップ

本ボードのメモリマップを以下に示します。本構成は、Linux を動作させる最小構成となっております。

表 5-1 SZ410-U00 メモリマップ

| Start Address   | End Address | ペリフェラル                   | デバイス               |

|-----------------|-------------|--------------------------|--------------------|

| $0x0000\ 00000$ | 0x03FF FFFF | PLB-DDR2 Controller      | DDR2 SDRAM 64Mbyte |

| 0x0400 0000     | 0xF0DF FFFF | Free                     |                    |

| 0xF0E0 0000     | 0xF0E0 FFFF | PLB-TEMAC                | Ether PHY          |

| 0xF0E1 0000     | 0xF0FE FFFF | Free                     |                    |

| 0xF0FF 0000     | 0xF0FF 01FF | OPB-SPI S                | フラッシュメモリ 8Mbyte    |

| 0xF0FF 0200     | 0xF0FF 1FFF | Free                     |                    |

| 0xF0FF 2000     | 0xF0FF 20FF | OPB-UART lite            | RS232C             |

| 0xF0FF 2100     | 0xF0FF 2FFF | Free                     |                    |

| 0xF0FF 3000     | 0xF0FF 30FF | OPB-Interrupt Controller |                    |

| 0xF0FF 3100     | 0xF0FF 9FFF | Free                     |                    |

| 0xF0FF A000     | 0xF0FF A1FF | OPB-GPIO                 | ブートモードジャンパ         |

|                 |             |                          | ソフトウェアリセット         |

| 0xF0FF A200     | 0xF0FF A3FF | OPB-GPIO                 | ユーザコントロール LED      |

| 0xF0FF A400     | 0xFFFF BFFF | Free                     |                    |

| 0xFFFF C000     | 0xFFFF FFFF | BRAM                     | BRAM 16KByte       |

# 6.FPGA ピンアサイン

FPGA( Xilinx Virtex-4 XC4VFX12 SF363 )の全ピンアサインを示します。

表 6-1 FPGA ピンアサイン 外部 I/O 関連(1/3)

| 番号  | バンク | 信号名                  | I/O | 用途     | 接続先  |

|-----|-----|----------------------|-----|--------|------|

| F15 | 1   | IO_L1P_D31_LC_1      | I/O | 外部 I/O | CON2 |

| E15 | 1   | IO_L1N_D30_LC_1      | I/O | IJ     | II . |

| E6  | 1   | IO_L2P_D29_LC_1      | I/O | IJ     | CON5 |

| F6  | 1   | IO_L2N_D28_LC_1      | I/O | JJ     | II.  |

| D15 | 1   | IO_L3P_D27_LC_1      | I/O | IJ     | CON2 |

| E14 | 1   | IO_L3N_D26_LC_1      | I/O | IJ     | II . |

| E7  | 1   | IO_L4P_D25_LC_1      | I/O | JJ     | CON5 |

| D6  | 1   | IO_L4N_D24_VREF_LC_1 | I/O | JJ     | II.  |

| D13 | 1   | IO_L5P_D23_LC_1      | I/O | IJ     | CON4 |

| C13 | 1   | IO_L5N_D22_LC_1      | I/O | IJ     | II . |

| C8  | 1   | IO_L6P_D21_LC_1      | I/O | JJ     | II.  |

| D8  | 1   | IO_L6N_D20_LC_1      | I/O | JJ     | II.  |

| D12 | 1   | IO_L7P_D19_LC_1      | I/O | IJ     | CON5 |

| C12 | 1   | IO_L7N_D18_LC_1      | I/O | IJ     | II . |

| C9  | 1   | IO_L8P_D17_CC_LC_1   | I/O | IJ     | II.  |

| D9  | 1   | IO_L8N_D16_CC_LC_1   | I/O | JJ     | II . |

| V10 | 2   | IO_L8P_D1_LC_2       | I/O | JJ     | CON2 |

| U9  | 2   | IO_L8N_D0_LC_2       | I/O | JJ     | II . |

表 6-2 FPGA ピンアサイン 外部 I/O 関連(2/3)

| 番号         | バンク | 信号名             | I/O | 用途     | 接続先  |

|------------|-----|-----------------|-----|--------|------|

| B6         | 6   | IO_L1P_6        | I/O | 外部 I/O | CON4 |

| A6         | 6   | IO_L1N_6        | I/O | 11     | ıı . |

| A5         | 6   | IO_L2P_6        | I/O | 11     | "    |

| B5         | 6   | IO_L2N_6        | I/O | 11     | ıı . |

| C6         | 6   | IO_L3P_6        | I/O | IJ     | CON3 |

| C5         | 6   | IO_L3N_6        | I/O | JJ     | ıı . |

| B4         | 6   | IO_L4P_6        | I/O | JJ     | ıı . |

| C4         | 6   | IO_L4N_VREF_6   | I/O | JJ     | ıı . |

| D5         | 6   | IO_L5P_6        | I/O | IJ     | II . |

| E5         | 6   | IO_L5N_6        | I/O | JJ     | ıı . |

| A3         | 6   | IO_L6P_6        | I/O | JJ     | ıı . |

| В3         | 6   | IO_L6N_6        | I/O | JJ     | ll   |

| D4         | 6   | IO_L7P_6        | I/O | IJ     | II . |

| D3         | 6   | IO_L7N_6        | I/O | JJ     | ll   |

| B2         | 6   | IO_L8P_CC_LC_6  | I/O | JJ     | ll   |

| C1         | 6   | IO_L8N_CC_LC_6  | I/O | JJ     | ll   |

| J4         | 6   | IO_L17P_6       | I/O | JJ     | ll . |

| <b>J</b> 3 | 6   | IO_L17N_6       | I/O | JJ     | ll   |

| H1         | 6   | IO_L18P_6       | I/O | JJ     | II . |

| G1         | 6   | IO_L18N_6       | I/O | JJ     | II . |

| J6         | 6   | IO_L19P_6       | I/O | JJ     | II . |

| J5         | 6   | IO_L19N_6       | I/O | JJ     | II . |

| Н3         | 6   | IO_L20P_6       | I/O | JJ     | II . |

| H2         | 6   | IO_L20N_VREF_6  | I/O | JJ     | ll   |

| K5         | 6   | IO_L21P_6       | I/O | IJ     | II . |

| K4         | 6   | IO_L21N_6       | I/O | JJ     | II . |

| K1         | 6   | IO_L22P_6       | I/O | JJ     | II . |

| J2         | 6   | IO_L22N_6       | I/O | IJ     | II . |

| L5         | 6   | IO_L23P_VRN_6   | I/O | IJ     | II . |

| L4         | 6   | IO_L23N_VRP_6   | I/O | IJ     | II . |

| K3         | 6   | IO_L24P_CC_LC_6 | I/O | JJ     | II . |

| K2         | 6   | IO_L24N_CC_LC_6 | I/O | IJ     | II . |

| F3         | 6   | IO_L9P_CC_LC_6  | I/O | JJ     | II . |

| E3         | 6   | IO_L9N_CC_LC_6  | I/O | JJ     | II . |

| С3         | 6   | IO_L10P_6       | I/O | JJ     | II . |

| C2         | 6   | IO_L10N_6       | I/O | JJ     | II . |

| F5         | 6   | IO_L11P_6       | I/O | JJ     | CON5 |

| F4         | 6   | IO_L11N_6       | I/O | 11     | 11   |

表 6-3 FPGA ピンアサイン 外部 I/O 関連(3/3)

| 番号 | バンク | 信号名             | I/O | 機能     | 接続先  |

|----|-----|-----------------|-----|--------|------|

| D2 | 6   | IO_L12P_6       | I/O | 外部 I/O | CON2 |

| E2 | 6   | IO_L12N_VREF_6  | I/O | IJ     | II.  |

| G5 | 6   | IO_L13P_6       | I/O | JJ     | II . |

| G4 | 6   | IO_L13N_6       | I/O | JJ     | II . |

| E1 | 6   | IO_L14P_6       | I/O | JJ     | II . |

| F1 | 6   | IO_L14N_6       | I/O | 11     | II . |

| H5 | 6   | IO_L15P_6       | I/O | 11     | II . |

| H4 | 6   | IO_L15N_6       | I/O | JJ     | II . |

| F2 | 6   | IO_L16P_6       | I/O | JJ     | II . |

| G2 | 6   | IO_L16N_6       | I/O | 11     | II . |

| M4 | 6   | IO_L25P_CC_LC_6 | I/O | 11     | II . |

| M3 | 6   | IO_L25N_CC_LC_6 | I/O | IJ     | II . |

| M1 | 6   | IO_L26P_6       | I/O | IJ     | II . |

| L1 | 6   | IO_L26N_6       | I/O | IJ     | II   |

| M6 | 6   | IO_L27P_6       | I/O | 11     | CON4 |

| M5 | 6   | IO_L27N_6       | I/O | IJ     | II . |

| M2 | 6   | IO_L28P_6       | I/O | JJ     | CON2 |

| L2 | 6   | IO_L28N_VREF_6  | I/O | 11     | II . |

| N5 | 6   | IO_L29P_6       | I/O | IJ     | II   |

| N4 | 6   | IO_L29N_6       | I/O | 11     | II . |

| N3 | 6   | IO_L30P_6       | I/O | IJ     | II.  |

| N2 | 6   | IO_L30N_6       | I/O | JJ     | II . |

| P5 | 6   | IO_L31P_6       | I/O | JJ     | II . |

| P4 | 6   | IO_L31N_6       | I/O | JJ     | II . |

| P2 | 6   | IO_L32P_6       | I/O | JJ     | II . |

| P1 | 6   | IO_L32N_6       | I/O | 11     | IJ   |

表 6-4 FPGA ピンアサイン 内部デバイス関連(1/4)

| 番号  | バンク | 信号名                | I/O | 機能             | 接続先           |

|-----|-----|--------------------|-----|----------------|---------------|

| A10 | 3   | IO L2P GC VRN LC 3 | I   | DCI 用終端抵抗      | 抵抗 51 Ω       |

| В9  | 3   | IO_L2N_GC_VRP_LC_3 | Ι   | DCI 用終端抵抗      | 抵抗 51 Ω       |

| C10 | 3   | SSTL REF           | I   | SSTLリファレンス     | +0.9V レギュレータ  |

| A14 | 3   | SD0 A0             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| A13 | 3   | SD0_A1             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| B14 | 3   | SD0_A2             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| A11 | 3   | SD0 A3             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| B8  | 3   | SD0 A4             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| B12 | 3   | SD0 A5             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| B10 | 3   | SD0 A6             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| A8  | 3   | SD0_A7             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| В7  | 3   | SD0_A8             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| B11 | 3   | SD0_A9             | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| B13 | 3   | SD0_A10            | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| C11 | 3   | SD0_A11            | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| A7  | 3   | SD0_A12            | I/O | DDR2 アドレスバス    | DDR2 SDRAM #0 |

| W13 | 4   | E_RX_DV            | I/O | MII            | Ether PHY     |

| W12 | 4   | E_RX_ER            | I/O | MII            | Ether PHY     |

| Y5  | 4   | IO_L2P_GC_LC_4     | I/O | DCI 用終端抵抗      | 抵抗 51 Ω       |

| W5  | 4   | IO_L2N_GC_LC_4     | I/O | DCI 用終端抵抗      | 抵抗 51 Ω       |

| Y12 | 4   | E_RXD0             | I/O | MII            | Ether PHY     |

| Y11 | 4   | E_RXD1             | I/O | MII            | Ether PHY     |

| Y6  | 4   | SYSCLK             | I/O | システムクロック入力     | 発振器:100MHz    |

| W6  | 4   | EEP_DO             | I/O | SPI            | EEPROM        |

| W11 | 4   | E_TXCLK            | I/O | MII            | Ether PHY     |

| W10 | 4   | E_MDC              | I/O | MII            | Ether PHY     |

| Y7  | 4   | IO_L6P_GC_LC_4     | I/O | 外部 I/O         | CON2          |

| W7  | 4   | IO_L6N_GC_LC_4     | I/O | 外部 I/O         | CON2          |

| Y10 | 4   | E_RX_CLK           | I/O | MII            | Ether PHY     |

| Y9  | 4   | E_RXD3             | I/O | MII            | Ether PHY     |

| W9  | 4   | E_MIO              | I/O | MII            | Ether PHY     |

| W8  | 4   | E_RXD2             | I/O | MII            | Ether PHY     |

| C17 | 5   | SSTL_REF           | I   | SSTLリファレンス     | +0.9V レギュレータ  |

| E19 | 5   | SSTL_REF           | I   | SSTLリファレンス     | +0.9V レギュレータ  |

| B15 | 5   | SD0_B1             | О   | DDR2 SDRAM B1  | DDR2 SDRAM #0 |

| A15 | 5   | SD0_B0             | O   | DDR2 SDRAM B0  | DDR2 SDRAM #0 |

| A16 | 5   | SD0_CK             | О   | DDR2 SDRAM CK  | DDR2 SDRAM #0 |

| B16 | 5   | SD0_CKn            | О   | DDR2 SDRAM CK  | DDR2 SDRAM #0 |

| C15 | 5   | SD0_ODT            | 0   | DDR2 SDRAM ODT | DDR2 SDRAM #0 |

| C16 | 5   | SD0_RASn           | 0   | DDR2 SDRAM RAS | DDR2 SDRAM #0 |

| B17 | 5   | SD0_CASn           | 0   | DDR2 SDRAM CAS | DDR2 SDRAM #0 |

| D16 | 5   | SD0_WEn            | О   | DDR2 SDRAM WE  | DDR2 SDRAM #0 |

### 表 6-5 FPGA ピンアサイン 内部デバイス関連(2/4)

| 番号  | バンク | 信号名           | I/O | 機能               | 接続先           |

|-----|-----|---------------|-----|------------------|---------------|

| A18 | 5   | SD0_D0        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| E16 | 5   | SD0_D1        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| C18 | 5   | SD0_D2        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| D17 | 5   | SD0_D3        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| F16 | 5   | SD0_D4        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| B18 | 5   | SD0_D5        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| D18 | 5   | SD0_D6        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| C19 | 5   | SD0_D7        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| F17 | 5   | SD0_LDM       | 0   | DDR2 SDRAM LDM   | DDR2 SDRAM #0 |

| B19 | 5   | SD0_LDQS      | I/O | DDR2 SDRAM LDQS  | DDR2 SDRAM #0 |

| C20 | 5   | SD0_LDQSn     | I/O | DDR2 SDRAM LDQS  | DDR2 SDRAM #0 |

| F20 | 5   | SD0_D8        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| D19 | 5   | SD0_D9        | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| H16 | 5   | SD0_D10       | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| G16 | 5   | SD0_D11       | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| G17 | 5   | SD0_D12       | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| E20 | 5   | SD0_D13       | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| F19 | 5   | SD0_D14       | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| H17 | 5   | SD0_D15       | I/O | DDR2 SDRAM データバス | DDR2 SDRAM #0 |

| G19 | 5   | SD0_UDM       | O   | DDR2 SDRAM UDM   | DDR2 SDRAM #0 |

| F18 | 5   | SD0_UDQS      | О   | DDR2 SDRAM UDQS  | DDR2 SDRAM #0 |

| E18 | 5   | SD0_UDQSn     | 0   | DDR2 SDRAM UDQS  | DDR2 SDRAM #0 |

| H19 | 5   | SSTL_REF      | I   | SSTLリファレンス       | +0.9V レギュレータ  |

| L19 | 5   | SSTL_REF      | I   | SSTLリファレンス       | +0.9V レギュレータ  |

| L16 | 5   | IO_L23P_VRN_5 | Ι   | DCI 用終端抵抗        | 抵抗 51 Ω       |

| L17 | 5   | IO_L23N_VRP_5 | Ι   | DCI 用終端抵抗        | 抵抗 51 Ω       |

| J17 | 5   | SD0_CSn       | О   | DDR2 SDRAM CS    | DDR2 SDRAM #0 |

| J18 | 5   | SD0_CKE       | О   | DDR2 SDRAM CKE   | DDR2 SDRAM #0 |

| H20 | 5   | SD1_UDM       | 0   | DDR2 SDRAM UDM   | DDR2 SDRAM #1 |

| M15 | 5   | SD1_LDM       | О   | DDR2 SDRAM データバス | DDR2 SDRAM #1 |

| M20 | 5   | SD1_CK        | О   | DDR2 SDRAM データバス | DDR2 SDRAM #1 |

| L20 | 5   | SD1_CKn       | О   | DDR2 SDRAM データバス | DDR2 SDRAM #1 |

| K18 | 5   | SD1_UDQS      | I/O | DDR2 SDRAM UDQS  | DDR2 SDRAM #1 |

| K19 | 5   | SD1_UDQSn     | I/O | DDR2 SDRAM UDQS  | DDR2 SDRAM #1 |

表 6-6 FPGA ピンアサイン 内部デバイス関連(3/4)

| 番号  | バンク | 信号名           | I/O | 機能                | 接続先           |

|-----|-----|---------------|-----|-------------------|---------------|

| H18 | 5   | SD1 D15       | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| G20 | 5   | SD1 D14       | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| J15 | 5   | SD1 D13       | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| J16 | 5   | SD1 D12       | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| K16 | 5   | SD1 D11       | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| K17 | 5   | SD1 D10       | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| K20 | 5   | SD1 D9        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| J19 | 5   | SD1 D8        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| P16 | 5   | SD1 D7        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| M16 | 5   | SD1 D6        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| N18 | 5   | SD1 D5        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| N16 | 5   | SD1 D4        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| N17 | 5   | SD1 D3        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| N19 | 5   | SD1 D2        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| M19 | 5   | SD1 D1        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| P17 | 5   | SD1 D0        | I/O | DDR2 SDRAM データバス  | DDR2 SDRAM #1 |

| P19 | 5   | SD1 CKE       | О   | DDR2 SDRAM CKE    | DDR2 SDRAM #1 |

| M17 | 5   | SD1_LDQS      | I/O | DDR2 SDRAM LDQS   | DDR2 SDRAM #1 |

| M18 | 5   | SD1_LDQSn     | I/O | DDR2 SDRAM LDQS   | DDR2 SDRAM #1 |

| T17 | 7   | SD1_CSn       | О   | DDR2 SDRAM CS     | DDR2 SDRAM #1 |

| R18 | 7   | SD1_B0        | О   | DDR2 SDRAM B0     | DDR2 SDRAM #1 |

| R17 | 7   | SD1_B1        | О   | DDR2 SDRAM B1     | DDR2 SDRAM #1 |

| U19 | 7   | SD1_CASn      | О   | DDR2 SDRAM CAS    | DDR2 SDRAM #1 |

| T15 | 7   | SD1_RASn      | О   | DDR2 SDRAM RAS    | DDR2 SDRAM #1 |

| U15 | 7   | SD1_ODT       | О   | DDR2 SDRAM ODT    | DDR2 SDRAM #1 |

| R16 | 7   | SD1_WEn       | О   | DDR2 SDRAM WE     | DDR2 SDRAM #1 |

| V20 | 7   | SSTL_REF      | I   | SSTL リファレンス       | +0.9V レギュレータ  |

| T18 | 7   | SD1_A10       | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| W17 | 7   | SD1_A0        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| R15 | 7   | SD1_A1        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| V17 | 7   | SD1_A2        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| U18 | 7   | SD1_A3        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| W18 | 7   | SD1_A4        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| Y17 | 7   | SD1_A5        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| V19 | 7   | SD1_A6        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| R19 | 7   | SD1_A7        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| R20 | 7   | SSTL_REF      | I   | SSTL リファレンス       | +0.9V レギュレータ  |

| U16 | 7   | SD1_A8        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| U17 | 7   | SD1_A9        | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| T19 | 7   | IO_L23P_VRN_7 | I   | DCI 用終端抵抗         | 抵抗 51 Ω       |

| T20 | 7   | IO_L23N_VRP_7 | I   | DCI 用終端抵抗         | 抵抗 51 Ω       |

| W19 | 7   | SD1_A11       | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

| V18 | 7   | SD1_A12       | I/O | DDR2 SDRAM アドレスバス | DDR2 SDRAM #1 |

### 表 6-7 FPGA ピンアサイン 内部デバイス関連(4/4)

| 番号 | バンク | 信号名           | I/O | 機能               | 接続先                   |

|----|-----|---------------|-----|------------------|-----------------------|

| U3 | 8   | RESET         | Ι   | システムリセット入力       | CPLD                  |

| U2 | 8   | FPGA_RESET_RQ | О   | 自己リセット出力         | CPLD                  |

| V2 | 8   | FR_CLK_1      | О   | SPI              | SPI フラッシュ             |

| V1 | 8   | FR_D          | О   | SPI              | SPI フラッシュ             |

| W3 | 8   | FR_DO         | I   | SPI              | SPI フラッシュ             |

| W2 | 8   | FR_CSn        | О   | SPI              | SPI フラッシュ             |

| W4 | 8   | JP_SET        | Ι   | ブートモード検出         | JP1                   |

| T4 | 8   | LED_RED       | О   | 電源 LED(赤)        | D1                    |

| U4 | 8   | CNSL_TXD      | Ι   | コンソール TXD        | RS-232Cトランシーバ =>CON1  |

| Y4 | 8   | CNSL_RXD      | О   | コンソール RXD        | RS-232Cトランシーバ =>CON1  |

| V4 | 8   | CNSL_RTS*     | О   | コンソール RTS        | RS-232Cトランシーバ =>CON1  |

| V3 | 8   | CNSL_CTS*     | Ι   | コンソール CTS        | RS-232C トランシーバ =>CON1 |

| R2 | 8   | EEP_DI        | О   | SPI              | EEPROM                |

| R1 | 8   | E_COL         | I   | MII              | Ether PHY             |

| T2 | 8   | nRST          | О   | Ether PHY リセット入力 | Ether PHY             |

| T1 | 8   | E_CRS         | I   | MII              | Ether PHY             |

| R4 | 8   | EEP_CS        | O   | SPI              | EEPROM                |

| R3 | 8   | EEP_SK        | O   | SPI              | EEPROM                |

| Т3 | 8   | E_TXD0        | О   | MII              | Ether PHY             |

| T6 | 8   | E_TX_ER       | O   | MII              | Ether PHY             |

| U6 | 8   | E_TXD2        | О   | MII              | Ether PHY             |

| U5 | 8   | E_TXD3        | О   | MII              | Ether PHY             |

| R6 | 8   | E_TXD1        | О   | MII              | Ether PHY             |

| R5 | 8   | E_TX_EN       | О   | MII              | Ether PHY             |

| 番号   | バンク | 信号名          | I/O | 機能          | 接続先          |

|------|-----|--------------|-----|-------------|--------------|

| Т9   |     | TCK FPGA_TCK | О   | JTAG        | CON7         |

| R9   |     | TDI FPGA_TDI | О   | JTAG        | CON7         |

| R10  |     | TDO FPGA_TDO | I   | JTAG        | CON7         |

| T8   |     | TMS FPGA_TMS | О   | JTAG        | CON7         |

| E9   |     | DIN          |     | コンフィギュレーション | CPLD         |

| E9   |     | DIN          |     | DIN         |              |

| E11  |     | CCLK         |     | コンフィギュレーション | CPLD         |

| E11  |     | CCLK         |     | CCLK        |              |

| F11  |     | DONE         |     | コンフィギュレーション | CPLD         |

| Г 11 |     | DONE         |     | DONE        |              |

| E12  |     | INIT B       |     | コンフィギュレーション | JP2, CPLD    |

| E1Z  |     | 11V11_D      |     | INIT_B      |              |

| R11  |     | CFG_M2       | I   | M2          | グランド         |

| T12  |     | CFG_M1       |     | M1          | グランド         |

| R12  |     | CFG_M0       |     | MO          | グランド         |

| E10  |     | PROGRAM_B    | I   | コンフィギュレーション | リセット回路, CPLD |

| F12  |     | PWR_RESETb   |     | PROGRAM_B   |              |

表 6-8 FPGA ピンアサイン JTAG、コンフィギュレーション関連

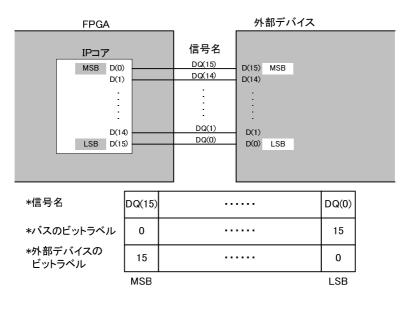

PowerPC405 はバスアーキテクチャとして IBM の CoreConnect を採用しています。CoreConnect のバスおよびレジスタビットの命名規則で MSB 側がビット(0)に定義されています。よって、DDR2 SDRAM データバス、アドレスバス、バンク等の VHDL バス記述は、MSB 側がビット(0)となっています。このため、LSB 側がビット(0)に定義されている外部デバイスと比べビットラベルが逆になります。上記表は通常の外部デバイスに接続するときのビットラベル(LSB 側がビット(0))で表記しています。アサイン時には十分ご注意ください。

図 6-1 CoreConnect のビットラベルと信号名

# 7.各種インターフェース仕様

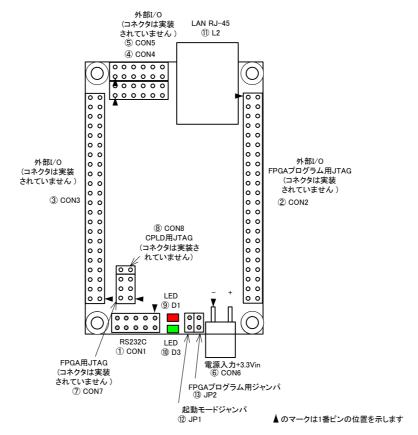

## 7.1.各種インターフェースの配置

図 7-1 各種インターフェースの配置

表 7-1 各種インターフェースの内容

|      | 部品番号 | 説明                                              |

|------|------|-------------------------------------------------|

| 1    | CON1 | RS-232C コネクタ                                    |

| 2    | CON2 | 外部 I/O、FPGA プログラム用 JTAG コネクタ Total I/Os 32PIN * |

| 3    | CON3 | 外部 I/O コネクタ Total I/Os 34PIN*                   |

| 4    | CON4 | 外部 I/O コネクタ Total I/Os 10PIN*                   |

| (5)  | CON5 | 外部 I/O コネクタ Total I/Os 10PIN*                   |

| 6    | CON6 | 電源入力+3.3V コネクタ                                  |

| 7    | CON7 | FPGA JTAG コネクタ                                  |

| 8    | CON8 | CPLD JTAG コネクタ                                  |

| 9    | D1   | ユーザコントロール LED 赤                                 |

| 10   | D3   | パワーオン LED 緑                                     |

| (11) | L2   | Ethernet 10/100 BASE-T コネクタ                     |

| 12   | JP1  | 起動モードジャンパ                                       |

| 13   | JP2  | FPGA プログラム用ジャンパ                                 |

<sup>\*</sup>外部 I/O ピンは FPGA と直結されているため、コンフィギュレーション中はハイインピーダンス状態となります。コンフィギュレーション後は設定値により任意の状態となります。

## 7.2. CON1 RS-232C

RS-232C コネクタです。レベルバッファを介して、FPGA と接続されています。ボード側で使用しているコネクタ型式/メーカは、A1-10PA-2.54DSA/ヒロセ(相当品)です。SUZAKU のデフォルトの FPGA プロジェクトでは、RTS と CTS をループバックして接続しています。

表 7-2 シリアルコンソールの設定

| 項目       | 設定        |

|----------|-----------|

| 転送レート    | 115.2kbps |

| データ      | 8bit      |

| パリティ     | なし        |

| ストップ bit | 1bit      |

| フロー制御    | なし        |

表 7-3 CON1 RS-232C

| 番号 | 信号名      | I/O | 機能                 |                |

|----|----------|-----|--------------------|----------------|

| 1  |          |     | 空き                 |                |

| 2  |          |     | 空き                 |                |

| 3  | RXD      | I   | Virtex-4 FX 接続ピン番号 | Y4(シリアルコンソール用) |

| 4  | RTS      | О   | Virtex-4 FX 接続ピン番号 | V4             |

| 5  | TXD      | О   | Virtex-4 FX 接続ピン番号 | U4(シリアルコンソール用) |

| 6  | CTS      | I   | Virtex-4 FX 接続ピン番号 | V3             |

| 7  |          |     | 空き                 |                |

| 8  |          |     | 空き                 |                |

| 9  | GND      |     | グランド               |                |

| 10 | +3.3VOUT | О   | 内部ロジック用電源出力+3.3V   |                |

# 7.3. CON2 外部 I/O、SPI フラッシュ用コネクタ

外部 I/O 及び SPI フラッシュ用コネクタです。

表 7-4 CON2 外部 I/O、SPI フラッシュ用 SPI コネクタ

| 番号 | 信号名             | I/O | 機能                        |     |

|----|-----------------|-----|---------------------------|-----|

| 1  | GND             |     | グランド                      |     |

| 2  | +3.3VOUT        | 0   | 内部ロジック用電源出力+3.3V          |     |

| 3  | EX_FR_CLK       | I   | SPI フラッシュプログラム用           |     |

| 4  | EX_FR_D         | I   | SPI フラッシュプログラム用           |     |

| 5  | EX_FR_DO        | 0   | SPI フラッシュプログラム用           |     |

| 6  | EX_FR_CSn       | I   | SPI フラッシュプログラム用           |     |

| 7  | IO_L3N_D26_LC_1 | I/O | 外部 I/O Virtec-4 接続ピン番号    | E14 |

| 8  | IO_L3P_D27_LC_1 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D15 |

| 9  | IO_L1N_D30_LC_1 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | E15 |

| 10 | IO_L1P_D31_LC_1 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | F15 |

| 11 | IO_L31N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | P4  |

| 12 | IO_L31P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | P5  |

| 13 | IO_L32N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | P1  |

| 14 | IO_L32P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | P2  |

| 15 | IO_L28N_VREF_6  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | L2  |

| 16 | IO_L28P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | M2  |

| 17 | IO_L30N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | N2  |

| 18 | IO_L30P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | N3  |

| 19 | GND             |     | グランド                      |     |

| 20 | IO_L6P_GC_LC_4  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | Y7  |

| 21 | GND             |     | グランド                      |     |

| 22 | IO_L6N_GC_LC_4  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | W7  |

| 23 | IO_L29N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | N4  |

| 24 | IO_L29P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | N5  |

| 25 | IO_L25N_CC_LC_6 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | M3  |

| 26 | IO_L25P_CC_LC_6 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | M4  |

| 27 | IO_L15N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | H4  |

| 28 | IO_L15P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | H5  |

| 29 | IO_L12N_VREF_6  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | E2  |

| 30 | IO_L12P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D2  |

| 31 | IO_L8N_D0_LC_2  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | U9  |

| 32 | IO_L8P_D1_LC_2  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | V10 |

| 33 | IO_L26N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | L1  |

| 34 | IO_L26P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | M1  |

| 35 | IO_L13N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | G4  |

| 36 | IO_L13P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | G5  |

| 37 | IO_L16N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | G2  |

| 38 | IO_L16P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | F2  |

| 39 | IO_L14N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | F1  |

| 40 | IO_L14P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | E1  |

| 41 | GND             |     | グランド                      |     |

| 42 | GND             |     | グランド                      |     |

| 43 | +3.3VIN         | I   | 電源入力+3.3V                 |     |

| 44 | +3.3VIN         | I   | 電源入力+3.3V                 |     |

# 7.4. CON3 外部 I/O コネクタ

外部 I/O コネクタです。

表 7-5 CON3 外部 I/O コネクタ

| 番号 | 信号名             | I/O | 機能                        |    |

|----|-----------------|-----|---------------------------|----|

| 1  | +3.3VIN         | I   | 電源入力+3.3V                 |    |

| 2  | +3.3VIN         | I   | 電源入力+3.3V                 |    |

| 3  | GND             |     | グランド                      |    |

| 4  | GND             |     | グランド                      |    |

| 5  | IO_L24P_CC_LC_6 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | K3 |

| 6  | IO_L24N_CC_LC_6 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | K2 |

| 7  | IO_L22P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | K1 |

| 8  | IO_L22N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | J2 |

| 9  | IO_L20P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | H3 |

| 10 | IO_L20N_VREF_6  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | H2 |

| 11 | IO_L23P_VRN_6   | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | L5 |

| 12 | IO_L23N_VRP_6   | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | L4 |

| 13 | IO_L21P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | K5 |

| 14 | IO_L21N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | K4 |

| 15 | IO_L19P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | J6 |

| 16 | IO_L19N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | J5 |

| 17 | IO_L18P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | H1 |

| 18 | IO_L18N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | G1 |

| 19 | IO_L9P_CC_LC_6  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | F3 |

| 20 | IO_L9N_CC_LC_6  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | E3 |

| 21 | IO_L10P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C3 |

| 22 | IO_L10N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C2 |

| 23 | IO_L2N_GC_LC_4  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | W5 |

| 24 | GND             |     | グランド                      |    |

| 25 | IO_L2P_GC_LC_4  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | Y5 |

| 26 | GND             |     | グランド                      |    |

| 27 | IO_L8P_CC_LC_6  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | B2 |

| 28 | IO_L8N_CC_LC_6  | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C1 |

| 29 | IO_L6P_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | A3 |

| 30 | IO_L6N_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | B3 |

| 31 | IO_L17P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | J4 |

| 32 | IO_L17N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | J3 |

| 33 | IO_L7P_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D4 |

| 34 | IO_L7N_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D3 |

| 35 | IO_L5P_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D5 |

| 36 | IO_L5N_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | E5 |

| 37 | IO_L4P_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | B4 |

| 38 | IO_L4N_VREF_6   | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C4 |

| 39 | IO_L3P_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C6 |

| 40 | IO_L3N_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C5 |

| 41 | NC              |     | 未接続                       |    |

| 42 | NC              |     | 未接続                       |    |

| 43 | +3.3VOUT        | O   | 内部ロジック用電源出力+3.3V          |    |

| 44 | GND             |     | グランド                      |    |

# 7.5. CON4 外部 I/O コネクタ

外部 I/O コネクタです。コネクタは実装されていません。

表 7-6 CON4 外部 I/O コネクタ

| 番号 | 信号名             | I/O | 機能                        |     |

|----|-----------------|-----|---------------------------|-----|

| 1  | NC              |     | 未接続                       |     |

| 2  | NC              |     | 未接続                       |     |

| 3  | IO_L2N_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | B5  |

| 4  | IO_L2P_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | A5  |

| 5  | IO_L1N_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | A6  |

| 6  | IO_L1P_6        | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | B6  |

| 7  | IO_L6N_D20_LC_1 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D8  |

| 8  | IO_L6P_D21_LC_1 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C8  |

| 9  | IO_L27N_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | M5  |

| 10 | IO_L27P_6       | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | M6  |

| 11 | IO_L5N_D22_LC_1 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C13 |

| 12 | IO_L5P_D23_LC_1 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D13 |

## 7.6.CON5 外部 I/O コネクタ

外部 I/O コネクタです。コネクタは実装されていません。

表 7-7 CON5 外部 I/O コネクタ

| 番号 | 信号名                  | I/O | 機能                        |     |

|----|----------------------|-----|---------------------------|-----|

| 1  | GND                  |     | グランド                      |     |

| 2  | +3.3VOUT             | O   | 内部ロジック用電源出力 +3.3V         |     |

| 3  | IO_L11N_6            | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | F4  |

| 4  | IO_L11P_6            | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | F5  |

| 5  | IO_L2N_D28_LC_1      | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | F6  |

| 6  | IO_L2P_D29_LC_1      | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | E6  |

| 7  | IO_L4N_D24_VREF_LC_1 | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D6  |

| 8  | IO_L4P_D25_LC_1      | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | E7  |

| 9  | IO_L8N_D16_CC_LC_1   | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D9  |

| 10 | IO_L8P_D17_CC_LC_1   | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C9  |

| 11 | IO_L7N_D18_LC_1      | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | C12 |

| 12 | IO_L7P_D19_LC_1      | I/O | 外部 I/O Virtex-4 FX 接続ピン番号 | D12 |

## 7.7.CON6 電源入力+3.3V コネクタ

電源入力コネクタです。電源入力+3.3Vは、+3.3V±3%で、単調増加としてください。

CON2、CON3の電源入力+3.3Vとボード内部で接続されています。

ボード側で使用しているコネクタ型式/メーカは、B2PS-VH/日本圧着端子(相当品)です。

ケーブル側のコネクタ型式/メーカは、ハウジング VHR-2N/日本圧着端子(相当品)、コンタクト BVH-21T-P1.1/日本圧着端子(相当品)または、BVH-41T-P1.1/日本圧着端子(相当品)が使用できます。

## 7.8. CON7 FPGA 用 JTAG コネクタ

FPGA 用 JTAG コネクタです。 JTAG の I/O の電圧は+3.3V です。 +3.3V に対応した JTAG ケーブルを使用してください。 3 ピン(TCK), 4 ピン(TMS)は CPLD にも接続されています。

| 番号 | 信号名      | I/O | 機能                |

|----|----------|-----|-------------------|

| 1  | GND      |     | グランド              |

| 2  | +3.3VOUT | О   | 内部ロジック用電源出力 +3.3V |

| 3  | TCK      | I   | JTAG              |

| 4  | TDI      | I   | JTAG              |

| 5  | TDO      | О   | JTAG              |

| 6  | TMS      | I   | JTAG              |

表 7-8 CON7 Virtex-4 FX 用 FPGA JTAG コネクタ

## 7.9. CON8 CPLD 用 JTAG コネクタ

CPLD 用 JTAG コネクタです。 JTAG の I/O の電圧は+3.3V です。 +3.3V に対応した JTAG ケーブルを使用してください。 TCK と TMS は CON7 の 3 ピン 4 ピンと共通で接続しています。

| 表 7-9 | CON8 Virt | ex-4 FX 用 | CPLD. | JTAG コネ | ヘクタ |

|-------|-----------|-----------|-------|---------|-----|

|       |           |           |       |         |     |

| 番号 | 信号名 | I/O | 機能   |

|----|-----|-----|------|

| 1  | TDI | I   | JTAG |

| 2  | TDO | О   | JTAG |

## 7.10. D1,D3 LED

ユーザーコントロール LED(赤)とパワーON LED(緑)です。

表 7-10 D1、D3 LED

| 信号名 | I/O | 機能                                   |

|-----|-----|--------------------------------------|

| D1  | O   | ユーザーコントロール LED Virtex-4 FX 接続ピン番号 T4 |

| D3  | O   | SUZAKU ボードに 3.3V が供給されると点灯           |

## 7.11. JP1,JP2 設定用ジャンパ

起動モード設定用ジャンパと FPGA プログラム用ジャンパです。

表 7-11 JP1、JP2 設定用ジャンパ

| 信号名 | I/O | 機能                                                                                                                                                                                                                                            |

|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1 | I   | 起動モードを切り替えるジャンパです。オープンでオートブート (SUZAKU 起動時に Linux が自動的に起動)します。ショートでブートローダモード(ブートローダのみを起動する場合に使用する)になります。 Virtex-4 FX 接続ピン番号 W4                                                                                                                 |

| JP2 |     | JTAG コネクタ(CON7)から FPGA にコンフィギュレーションデータを<br>ダウンロードする時および SPI フラッシュ用コネクタ(CON2)からコン<br>フィギュレーションデータを SPI フラッシュメモリにダウンロードすると<br>きに使用するジャンパです。本ジャンパをショートすると、電源再投入<br>時 FPGA に対し、コンフィギュレーションを停止させることができ、そ<br>の時にコンフィギュレーションデータをダウンロードすることができま<br>す。 |

## 7.12. SUZAKU L2 Ethernet 10/100BASE-T

ボード側で使用しているコネクタ型式/メーカは、J0026D21B/PULSEです。

表 7-12 L2 Ethernet 10/100 BASE-T

| 番号 | 信号名 | I/O | 機能                         |

|----|-----|-----|----------------------------|

| 1  | TX+ |     | 差動ツイストペア出力+                |

| 2  | TX- |     | 差動ツイストペア出力・                |

| 3  | RX+ |     | 差動ツイストペア入力+                |

| 4  |     |     | 75Ω終端(4番ピンと5番ピンはショートしています) |

| 5  |     |     | 75Ω終端(4番ピンと5番ピンはショートしています) |

| 6  | RX- |     | 差動ツイストペア入力・                |

| 7  |     | •   | 75Ω終端(7番ピンと8番ピンはショートしています) |

| 8  |     |     | 75Ω終端(7番ピンと8番ピンはショートしています) |

# 8.基板形状図

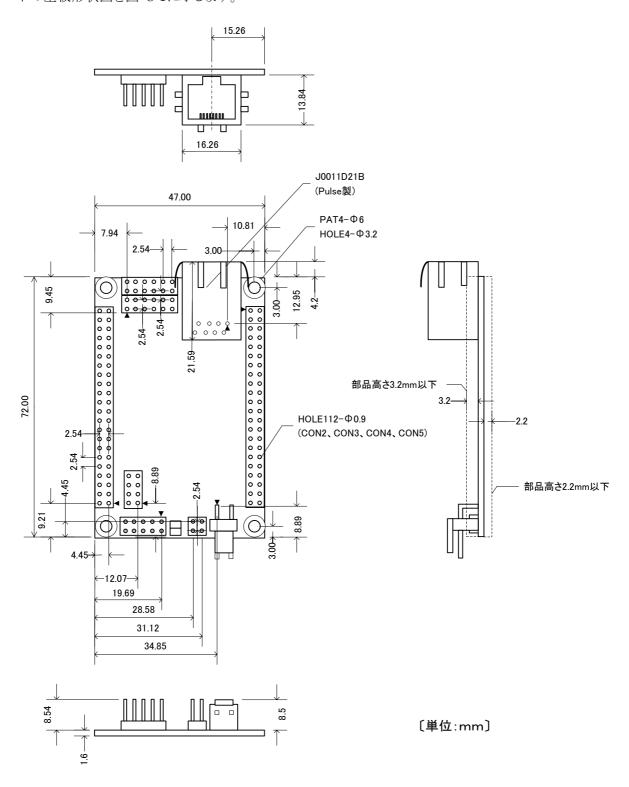

本ボードの基板形状図を図 8-1に示します。

図 8-1 SZ410-U00 の基板形状

#### 改訂履歴

| Ver.  | 年月日        | 改訂内容  |

|-------|------------|-------|

| 1.0.0 | 2007/10/10 | •初版作成 |

| 1.0.1 | 2007/10/19 | •誤記訂正 |

SUZAKU-V Hardware Manual

2007年10月19日 Version 1.0.1

TEL: 011-207-6550 FAX: 011-207-6570

株式会社アットマークテクノ

060-0035 札幌市中央区北 5 条東 2 丁目 AFT ビル 6F