# SUZAKU Starter Kit スターターキットガイド

(FPGA開発編)

Version 2.2.0

SZ130-SIL SZ310-SIL SZ410-SIL

株式会社アットマークテクノ

http://www.atmark-techno.com/

SUZAKU 公式サイト

http://suzaku.atmark-techno.com/

# はじめに

この度は、『SUZAKU スターターキット』をお買い上げいただきありがとうございます。

本スターターキットは、FPGA 搭載ボード"SUZAKU"を初めて手に取る方にもお使いいただけるよう、第一歩を踏み出すために必要な機材をセットにした学習用キットです。

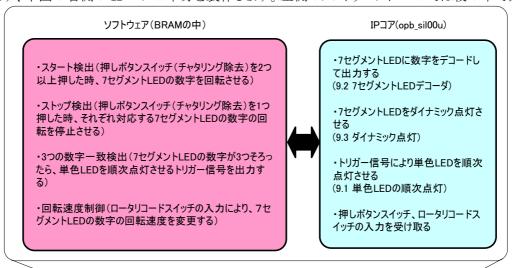

"SUZAKU"は FPGA(Field Programmable Gate Array)を搭載した組み込み機器開発ボードです。FPGAとは簡単にいうとプログラミングすることができる LSI のことで、さまざまな設計データを送り込んで再構築させることが可能なデバイスです。

この FPGA は近年、より大規模化・低価格化してきています。現在では容易に入手できる FPGA ひとつで、内部にプロセッサと複数の必要な周辺回路を同時に構成するといったことが可能となっています。例えば UART がいくつも欲しい、GPIO ポートが大量に必要だ、画像処理を高速に行うための回路を投入したい、さらに、プロセッサを 2 つ持ちたいといった場合ですら、回路規模が許す限り自由に構成することが可能なのです。

"SUZAKU"は、この FPGA の利点を最大限に生かすべく誕生した小型 FPGA ボードです。 "SUZAKU"の特徴を以下に挙げます。

- 固定された外部インターフェースとして、Ethernet と RS-232C を持っています。

- マイクロコンピュータボードとして動作するために必要な要素であるクロック、DRAM、フラッシュメモリ、 Ethernet MAC/Phy、RS-232Cドライバルシーバが、基板上に実装されています。

- 電源は+3.3V 単一入力です。内部に FPGA 用の電源である 2.5V、1.2V を作る回路が組み込まれています。 また、FPGA を再コンフィギュレーション可能にするための回路が組み込まれています。

- 基板の外周に沿って 86 個 (SZ310-U00 は 70 個) の空きピンが備えられています。 これらはすべて FPGA の I/O ピンに結線されており、外部デバイスや装置との接続のため自由に使用することができます。

- FPGA の中ではソフトプロセッサ (MicroBlaze) もしくはハードプロセッサ (PowerPC) が動いています。

- フラッシュメモリの中には、OS(Linux)、Ethernet などのデバイスドライバ、アプリケーション群が書き込まれており、電源を入れるだけでこれらを利用することができるようになっています。

- 高機能である Linux を使用しながら、同時にリアルタイム処理を行うような用途向けに構成することも可能です。

- 〇 基板上には SDRAM が 2 枚実装されており、これらを FPGA 内に構成した 2 つの CPU から独立して使用させることができるため、片方で Linux を、他方でリアルタイム OS を動作させる、といった使い方ができます。 \*\*

以上のように"SUZAKU"は、FPGA が持つ柔軟性と、Linux が持つ高機能性、豊富なソフトウェア資産等これらの利点を同時に享受することができるプラットフォームです。これらの特徴を利用することにより、旧来の開発手法に比べて開発期間を短縮し、コストダウンを実現することができます。

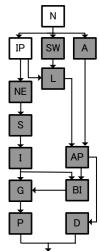

"SUZAKU"上での開発作業の流れは、

- ① FPGA 開発

- ② ソフトウェア開発

の2段階に大きく分けることができます。本書ではこのうち①FPGA 開発について、実際に"SUZAKU スターターキット"を使用しながら解説していきます。②ソフトウェア開発については、本書と対となる"SUZAKU スターターキットガイド(Linux 開発編)"をご参照ください。

本書を足掛かりとして、SUZAKU 開発者のスペシャリストを目指していただければ幸いです。

i

<sup>\*</sup> SDRAM が2枚実装されているのはSZ130-U00 およびSZ410-U00です。

## ・対象となる読者

本書は SUZAKU の FPGA 開発者向けに書かれた入門書です。 SUZAKU の FPGA には初めからプロセッサ が搭載されており、ディジタル回路、プロセッサ、バス、メモリ等様々な要素が絡み合ってきます。 このため、どこで何 が行われているのか分からない、やりたいことがあっても、それを実現するためにはどこをどうすればよいのか分からないという方もおられると思います。

本書では、どこから手をつけていいか分からない方、SUZAKU をはじめて使う方、SUZAKU での FPGA 開発方法について丁寧で分かりやすい説明を望む方を対象としています。

### ・本書の構成

本書では、SUZAKU スターターキットを使用してスロットマシンを製作しながら、SUZAKU の使い方について解説してきます。内容は3部構成となっています。

第 1 部では SUZAKU で FPGA 開発を行うために必要な知識や準備について説明をします。 SUZAKU および LED/SW ボードについて(第1、2、3 章)と、作業の前に必要な準備と簡単な SUZAKU の使い方(第 4、5、6 章)を 説明します。

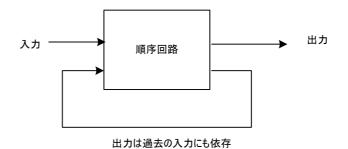

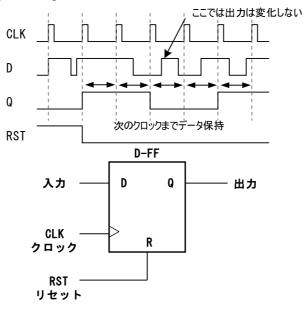

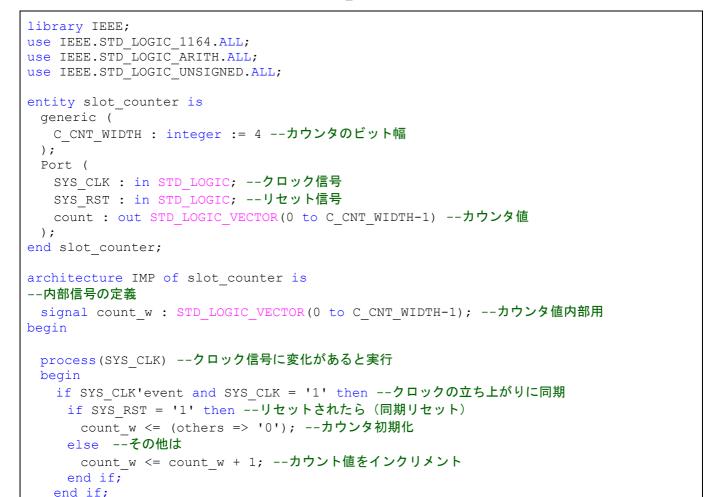

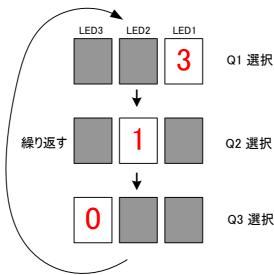

第2部では Xilinx の ISE というツールを用い、プロセッサを含まない FPGA の開発を実際に SUZAKU スターターキットを用いて体験します。まず、単色 LED を1つだけ点灯する簡単な回路の作成から始まり(第7章)、組み合わせ回路、順次回路の説明をし(第8章)、これらを踏まえて、スロットマシンの要素となる回路(単色 LED 順次点灯回路、7セグメント LED デコーダ回路、ダイナミック点灯回路)を作成していきます(第9章)。

第3部では Xilinx の EDK というツールを用い、プロセッサを含んだ FPGA の開発を実際に SUZAKU スターターキットを用いて体験します。まずは EDK がどのようなツールであるのかを説明し、SUZAKU のデフォルトの構成を説明します(第10章)。 その後、ISE で作成した回路を IP コアにして SUZAKU と接続し、スロットマシンを完成させます(第11章)。 最後に、こんなこともやってみよう、という例を示します(第12章)。

スロットマシンを最後までつくり上げる頃には、SUZAKU の効果的な使い方を学んでいただけたるのではないかと思います。

# 表記について

本書は SUZAKU-S(SZ010-U00、SZ030-U00、SZ130-U00)、SUZAKU-V(SZ310-U00、SZ410-U00)を対象 に書かれています。 内容によってはすべての SUZAKU に当てはまらない場合がございます。 当てはまらないものが ある場合は以下の記号で対象となる SUZAKU を示します。

# SZ010 SZ030 SZ130 SZ310 SZ410

また、これ以降型番の-U00を省略して表記します。

本書では以下のようにフォントを使っています。

| フォント例            | 説明        |

|------------------|-----------|

| 本文中のフォント         | 本文        |

| SUZAKU %         | プロンプトの文字列 |

| std_logic_vector | VHDL 記述   |

| #include         | C言語記述     |

# 注意事項

# ・安全に関する注意事項

SUZAKU スターターキットを安全にご使用いただくために、特に以下の点にご注意くださいますようお願いいたします。

本製品には一般電子機器用(OA機器・通信機器・計測機器・工作機械等)に製造された半導体部品を使用していますので、その誤作動や故障が直接生命を脅かしたり、身体・財産等に危害を及ぼす恐れのある装置(医療機器・交通機器・燃焼制御・安全装置等)に組み込んで使用したりしないでください。また、半導体部品を使用した製品は、外来ノイズやサージにより誤作動したり故障したりする可能性があります。ご使用になる場合は万一誤作動、故障した場合においても生命・身体・財産等が侵害されることのないよう、装置としての安全設計(リミットスイッチやヒューズ・ブレーカ等の保護回路の設置、装置の多重化等)に万全を期されますようお願い申しあげます。発熱により高温になる部品があります。周囲温度や取り扱いによってはやけどの恐れがあります。電源が入っている状態および電源切断後しばらくは本製品に触れないようお願い申しあげます。

# ・保証に関する注意事項

### ● 製品保証範囲について

付属品(ソフトウェアを含みます)を使用し、取扱説明書、各注意事項に基づく正常なご使用に限り有効です。 万一正常なご使用のもと製品が故障した場合は、初期不良保証期間内であれば新品交換をさせていただきます。

### ● 保証対象外になる場合

次のような場合の故障・損傷は、保証期間内であっても保証対象外になります。

- 1. 取扱説明書記載の使用方法、または注意に反したお取り扱いによる場合

- 2. 改造・調整や部品交換による場合。または正規のものを使用していないか、あるいは過去に使用されていた場合

- 3. お客様のお手元に渡った後の輸送、移動時の落下等お取り扱いの不備による場合

- 4. 火災・地震・水害・落雷・その他の天災、公害や異常電圧による場合

- 5. AC アダプタ・ケーブル等の付属品について、同梱のものを使用していない場合

- 6. 付属品がすべて揃っていない場合

### ● 免責事項

弊社に故意または重大な過失があった場合を除き、製品の使用および、故障、修理によって発生するいかなる損害についても、一切の責任を負わないものとします。

本製品は購入時の初期不良以外の保証を行っておりません。保証期間は商品到着後2週間です。本製品をご購入しましたらお手数でも必ず動作確認を行ってからご使用ください。本製品に対して注意事項を守らずに発生した故障につきましては保証対象外となります。

### ・取り扱い上の注意事項

劣化、破損、誤動作、発煙、発火の原因となることがあります。取り扱い時には以下のような点にご注意ください。

### ● 入力電源

5V+5%以上の電圧を入力する、極性を間違う等しないでください。また、SUZAKU の+3.3V 外部入力 (CON6)に電源を供給しないでください。

### ● インターフェース

各インターフェース(外部 I/O、RS-232C、Ethernet、JTAG)には規定以外の信号を接続しないでください。また、信号の極性、入出力方向を間違わないでください。

### ● 本製品の改造

本製品について改造を行った場合は保証対象外となりますので、十分にご注意ください。(※コネクタ非搭載箇所へのコネクタの増設を除く。)

コネクタを増設する際にはマスキングを行い、周囲の部品に半田くず、半田ボール等付着しない様十分にご 注意ください。

なお、改造を行う場合は、改造前の動作確認を必ず行うようお願いします。

### ● FPGA プログラム

周辺回路(ボード上の部品も含む)と信号の衝突(同じ信号に 2 つのデバイスから出力する)を起こすような FPGA プログラムを行わないでください。 FPGA のプログラムを間違わないでください。

### ● 電源の投入

本ボードや周辺回路に電源が入っている状態では絶対に FPGA I/O、JTAG 用コネクタの着脱を行わないでください。

### ● 静電気

本ボードには CMOS デバイスを使用していますので、ご使用になるまでは帯電防止対策のされている、 出荷時のパッケージ等にて保管してください。

### ● ラッチアップ

電源および入出力からの過大なノイズやサージ、電源電圧の急激な変動等で、使用している CMOS デバイスがラッチアップを起こす可能性があります。いったんラッチアップ状態となると、電源を切断しないかぎりこの状態が維持されるため、デバイスの破損につながることがあります。ノイズの影響を受けやすい入出力ラインには保護回路を入れる、ノイズ源となる装置と共通の電源を使用しない等の対策をとることをお勧めします。

### ● 衝撃、振動

落下や衝突などの強い衝撃や、強い振動、遠心力を与えないでください。振動部や回転部などへの搭載はしないでください。

### ● 高温低温、多湿

極度に高温や低温になる環境や、湿度が高い環境では使用しないでください。

### ● 塵埃

塵埃の多い環境では使用しないでください。

# · FPGA 使用に関しての注意事項

本製品に含まれる FPGA プロジェクト(付属のドキュメント等も含む)は、現状のまま(AS IS)提供されるものであり、特定の目的に適合することや、その信頼性、正確性を保証するものではありません。また、本製品の使用による結果について、なんら保証するものではありません。

本製品は、ベンダのツール(Xilinx 製 EDK、ISE やその他ベンダツール)やベンダの IP コアを利用し、FPGA プロジェクトの構築、コンパイル、コンフィギュレーションデータの生成を行っておりますが、これらツールに関しての販売、サポート、保証等は行っておりません。

# ・ソフトウェア使用に関しての注意事項

本製品に含まれるソフトウェア(付属のドキュメント等も含みます)は、現状のまま(AS IS)提供されるものであり、特定の目的に適合することや、その信頼性、正確性を保証するものではありません。また、本製品の使用による結果について、なんら保証するものではありません。

# 目次

| d City Attit ) - Aug       | _  |

|----------------------------|----|

| 1. SUZAKU について             |    |

| 1.1. SUZAKU の特徴            |    |

| 1.2. 仕様                    |    |

| 1.3. 全体ブロック図               |    |

| 1.3.1. SZ010, SZ030        |    |

| 1.3.2. SZ130               |    |

| 1.3.3. SZ310               |    |

| 1.3.4. SZ410               |    |

| 1.4. メモリマップ                |    |

| 1.4.1. SZ010, SZ030        |    |

| 1.4.2. SZ130               |    |

| 1.4.3. SZ310               |    |

| 1.4.4. SZ410               |    |

| 2. LED/SW ボードについて          |    |

| 2.1. 回路説明                  |    |

| 2.2. ピンアサイン                |    |

| 3. SUZAKU+LED/SW ボードの構成    |    |

| 3.1. 各種インターフェースの配置         | 21 |

| 4. 電源を入れる前に                | 23 |

| 4.1. 必要なもの                 | 23 |

| 4.2. 開発環境                  | 24 |

| 4.3. 付属 CD-ROM について        | 25 |

| 4.4. 組み立て                  | 26 |

| 5. SUZAKU+LED/SW ボードを動かす   |    |

| 5.1. 接続方法                  |    |

| 5.2. シリアル通信ソフトウェア          |    |

| 5.3. ブートローダモードでスロットマシンを動かす |    |

| 5.3.1. 電源について              |    |

| 5.3.2. スロットマシン起動           |    |

| 5.4. オートブートモードで Linux を動かす |    |

| 5.4.1. Linux の起動           |    |

| 5.4.2. ログイン                |    |

| 5.4.3. ネットワークの設定           |    |

|                            |    |

| 5.4.4. ウェブ                 |    |

| 5.4.5. 終了方法                |    |

| 5.5. SUZAKU のブートシーケンス      |    |

| 6. SUZAKU を書き換える           |    |

| 6.1. フラッシュメモリマップ           |    |

| 6.1.1. SZ130               |    |

| 6.1.2. SZ010               |    |

| 6.1.3. SZ030, SZ310        |    |

| 6.1.4. SZ410               |    |

| 6.2. FPGA の書き換えかた          |    |

| 6.2.1. iMPACT で書き換える       |    |

| 6.2.2. LBPlayer2 で書き換える    |    |

| 6.2.3. SPI Writer で書き換える   |    |

| 6.3. ブートローダ Hermit の書き換えかた |    |

| 6.3.1. BBoot で書き換える        |    |

| 6.4. Linux の書き換えかた                                   |    |

|------------------------------------------------------|----|

| 6.4.1. ダウンローダ Hermit で書き換える                          | 75 |

| 7. ISEの使い方                                           |    |

| 7.1. 単色 LED を点灯させる                                   |    |

| 7.1.1. 単色 LED 周辺回路                                   |    |

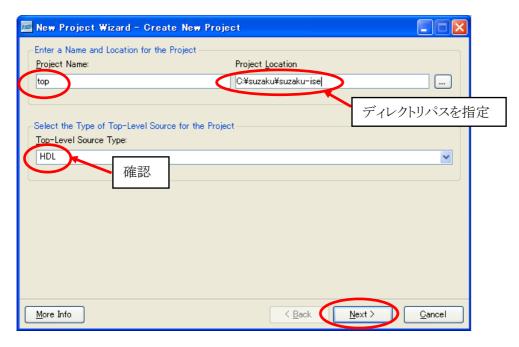

| 7.2. プロジェクトの新規作成                                     |    |

| 7.2.1. プロジェクト作成                                      |    |

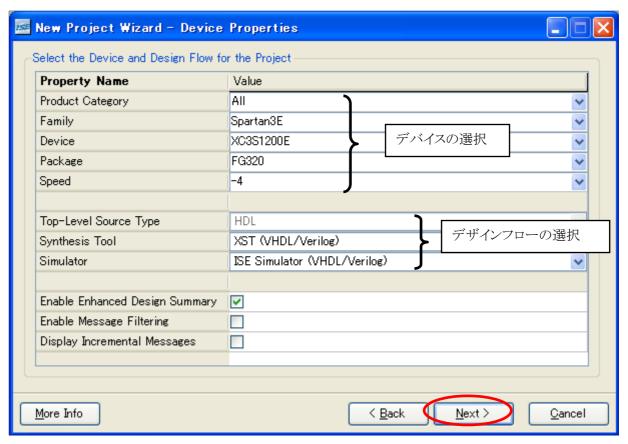

| 7.2.2. デバイスの選択                                       |    |

| 7.2.3. ソースファイル作成                                     |    |

| 7.3. ソースファイル作成                                       |    |

| 7.4. 論理合成                                            |    |

| 7.5. インプリメンテーション                                     |    |

| 7.6. プログラムファイル作成                                     |    |

| 7.7. コンフィギュレーション                                     |    |

| 7.7.1. JTAG でコンフィギュレーション                             |    |

| 7.7.2. フラッシュメモリに保存してコンフィギュレーション                      |    |

| 7.8. 空きピン処理                                          |    |

| 8. VHDL によるロジック設計                                    |    |

| 8.1. VHDL の基本構造                                      |    |

| 8.2. ライブラリ宣言とパッケージ呼び出し                               |    |

| 8.3. エンティティ(entity)                                  |    |

| 8.4. アーキテクチャ(architecture)                           |    |

| 8.5. 組み合わせ回路(not、and、or)                             |    |

| 8.5.1. 押しボタンスイッチ周辺回路                                 |    |

| 8.5.2. not、and、or を使う                                |    |

| 8.6. 順序回路                                            |    |

| 8.6.1. D-FF(D 型フリップフロップ)                             |    |

| 8.6.2. 同期設計                                          |    |

| 8.6.3. カウンタ                                          |    |

| 8.7. ISE Simulator の使い方                              |    |

| 8.7.1. プロジェクトの新規作成                                   |    |

| 8.7.2. テストベンチの新規作成                                   |    |

| 8.7.3. シミュレーション実行                                    |    |

| 9. FPGA 入門 スロットマシン製作                                 |    |

| 9.1. 単色 LED の順次点灯                                    |    |

| 9.1.1. 単色 LED 周辺回路                                   |    |

| 9.1.2. プロジェクト新規作成、論理合成                               |    |

| 9.1.3. シミュレーション                                      |    |

| 9.1.4. 再度論理合成                                        |    |

| 9.1.5. インプリメンテーション                                   |    |

| 9.1.6. プログラムファイル作成、コンフィギュレーション                       |    |

| 9.1.7. バスのビットラベルについて                                 |    |

|                                                      |    |

| 9.2.1. ロータリコードスイッチ周辺回路                               |    |

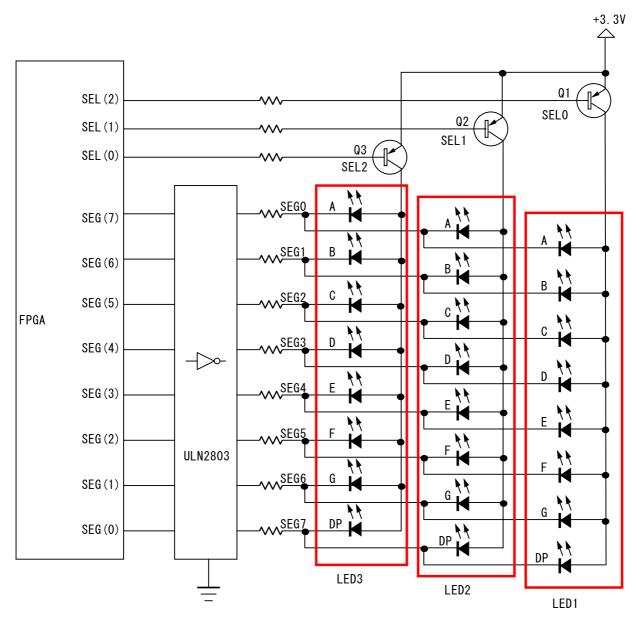

| 9.2.2. 7 セグメント LED 周辺回路                              |    |

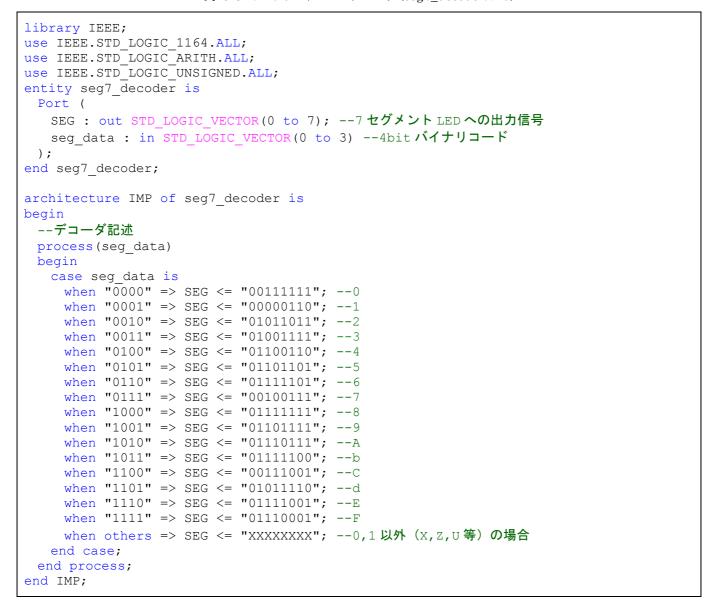

| 9.2.3. プロジェクト新規作成、論理合成                               |    |

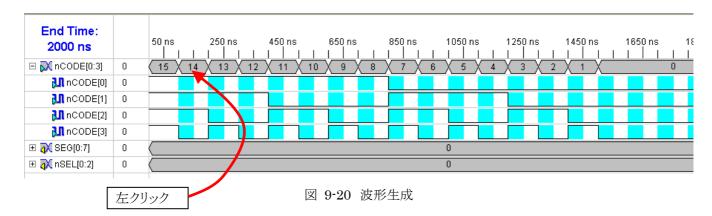

| 9.2.4. シミュレーション                                      |    |

| 9.2.5. インプリメンテーション<br>9.2.6. プログラムファイル作成、コンフィギュレーション |    |

| 9.2.6. プログプムノデイル作成、コンノイキュレーション<br>9.3. ダイナミック点灯      |    |

| 9.3. タイナミツケ点灯                                        |    |

| ひ.ひ.1. 1 5.7 7マココカカカリルタリニルは                          |    |

| 9.3.2. プロジェクト新規作成、論理合成                  | 138 |

|-----------------------------------------|-----|

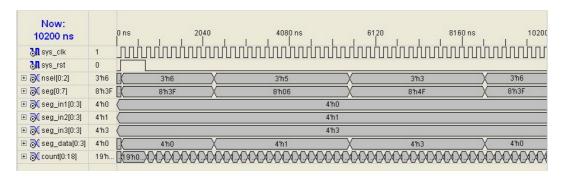

| 9.3.3. シミュレーション                         | 142 |

| 9.3.4. インプリメンテーション                      | 142 |

| 9.3.5. プログラムファイル作成、コンフィギュレーション          | 142 |

| 10. EDK の使い方                            | 143 |

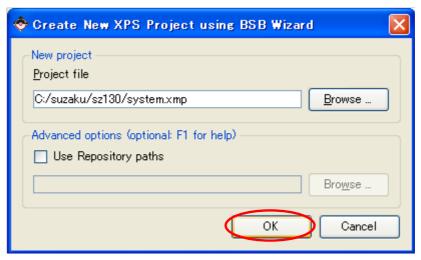

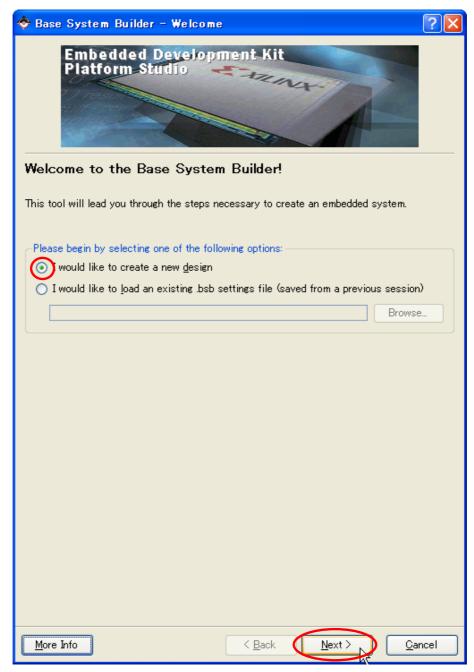

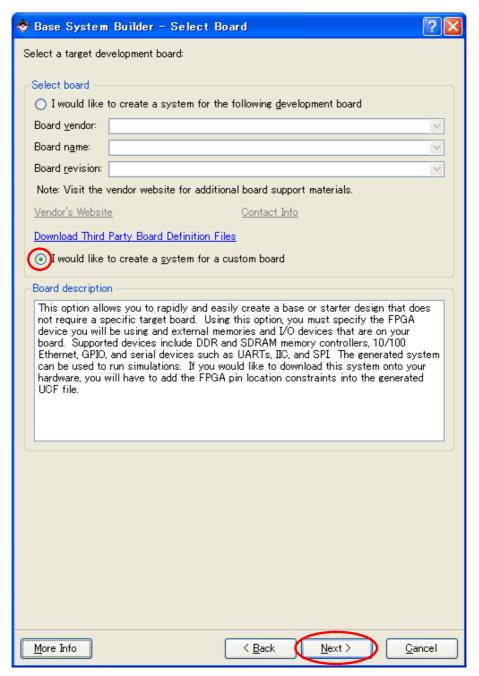

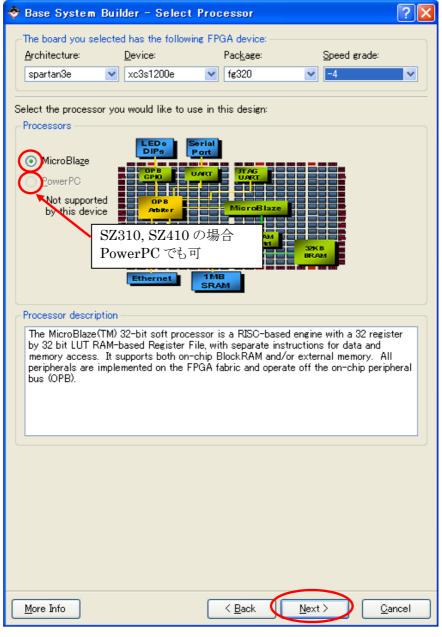

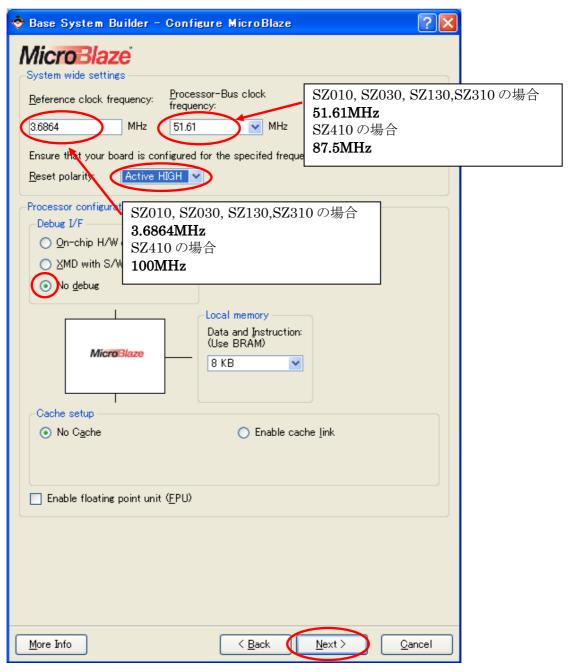

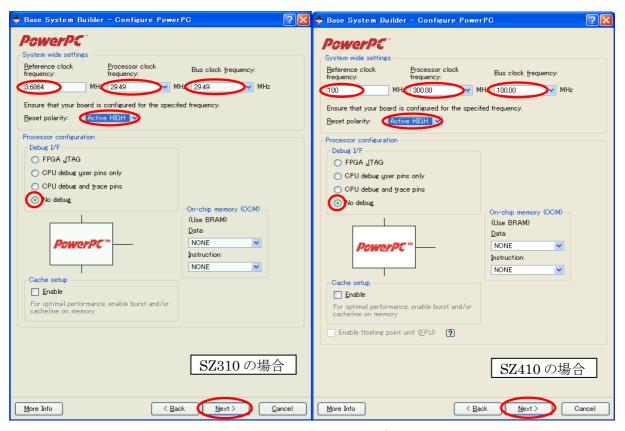

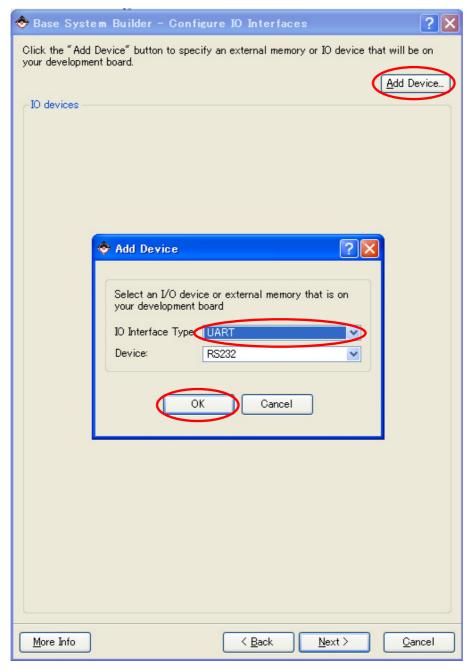

| 10.1. BSB ではじめての MicroBlaze & PowerPC   | 144 |

| 10.1.1. BSB                             | 145 |

| 10.1.2. XPS ハードウェア設定                    | 159 |

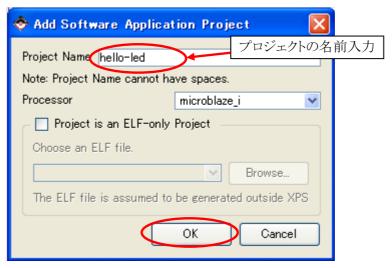

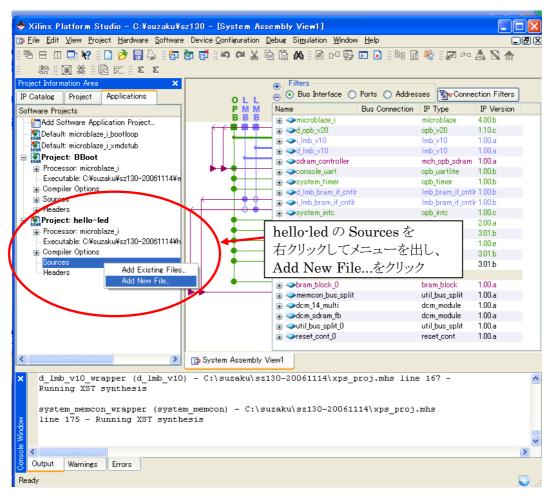

| 10.1.3. XPS アプリケーション作成                  | 163 |

| 10.1.4. プログラムファイルを作成してコンフィギュレーション       | 167 |

| 10.2. SUZAKU のデフォルト                     | 169 |

| 10.2.1. SZ010, SZ030 の構成                | 170 |

| 10.2.2. SZ130 の構成                       | 171 |

| 10.2.3. SZ310 の構成                       | 172 |

| 10.2.4. SZ410 の構成                       | 173 |

| 10.2.5. IP コア                           | 174 |

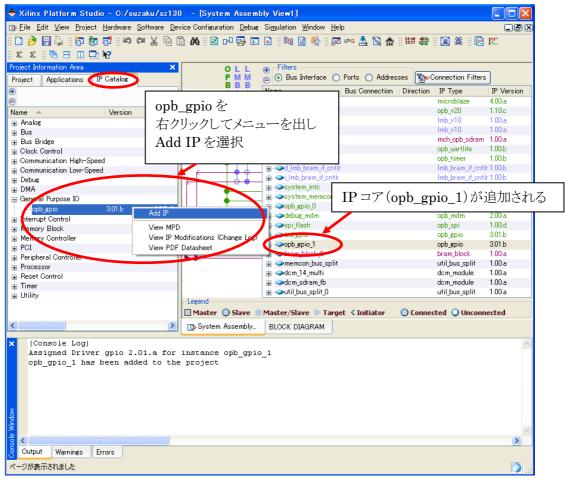

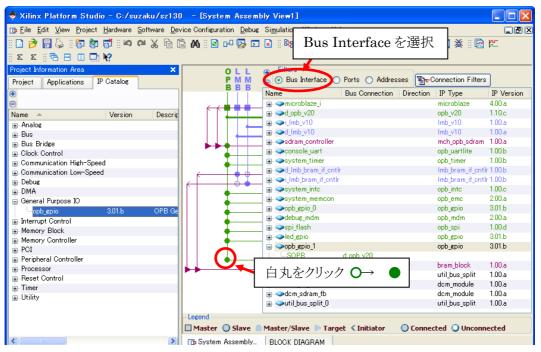

| 10.3. GPIO の追加                          | 178 |

| 10.3.1. GPIO の接続                        | 178 |

| 10.3.2. ハードウェア設定                        | 179 |

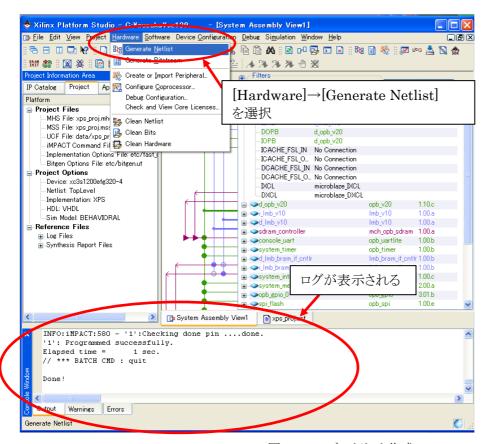

| 10.3.3. ネットリスト, プログラムファイル(Hard のみ) 作成   | 188 |

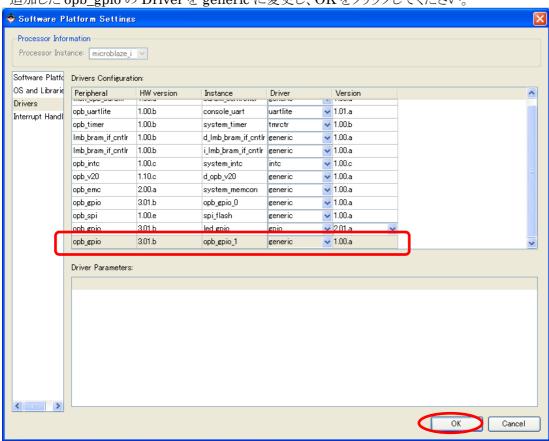

| 10.3.4. ソフトウェア設定                        | 189 |

| 10.3.5. アプリケーション編集                      |     |

| 10.3.6. アプリケーション生成                      | 197 |

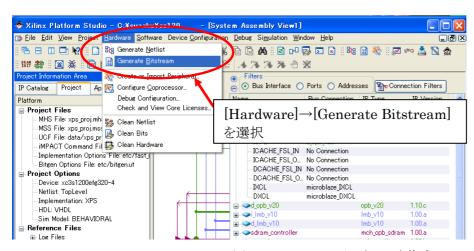

| 10.3.7. プログラムファイル作成                     |     |

| 10.3.8. コンフィギュレーション                     |     |

| 10.3.9. 空きピン処理                          |     |

| 10.4. UART の追加                          |     |

| 10.4.1. ハードウェア設定                        |     |

| 10.4.2. ネットリスト, プログラムファイル(Hard のみ) 作成   |     |

| 10.4.3. ソフトウェア設定                        |     |

| 10.4.4. アプリケーション編集                      |     |

| 10.4.5. アプリケーション生成                      |     |

| 10.4.6. プログラムファイル作成                     | 214 |

| 10.4.7. コンフィギュレーション                     |     |

| 11. スロットマシンのコアを CPU で制御する               |     |

| 11.1. ウィザードを使って OPB インターフェースをつくる        |     |

| 11.2. 今まで作ってきた回路をまとめる                   |     |

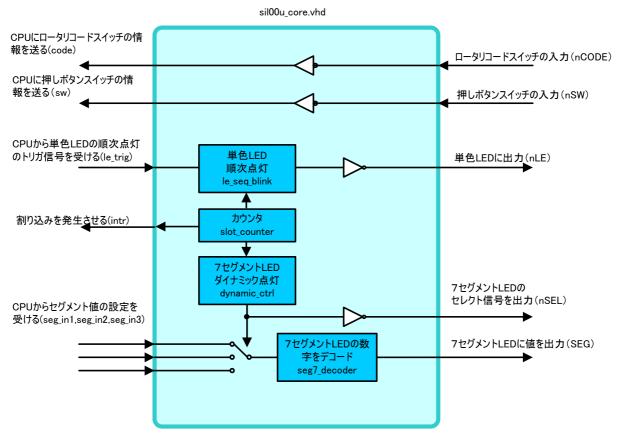

| 11.2.1. sil00u_core.vhd.                |     |

| 11.3. OPB インターフェースとコアを接続し、自作 IP コアを仕上げる |     |

| 11.3.1. user_logic.vhd.                 |     |

| 11.3.2. opb_sil00u.vhd                  |     |

| 11.3.3. opb_sil00u_v2_1_0.mpd           | 236 |

| 11.3.4. opb_sil00u_v2_1_0.pao           | 237 |

| 11.3.5. opb_sil00u.c                    |     |

| 11.4. 自作 IP コアの追加                       |     |

| 11.4.1. SZ010、SZ030 の場合                 | 238 |

| 11.4.2. SZ130 の場合                       | 239 |

| 11.4.3. SZ310 の場合                       |     |

| 11.4.4. SZ410 の場合                       |     |

| 11.4.5. ハードウェア設定                        |     |

| 11.4.6. ネットリスト, プログラムファイル(Hard のみ) 作成   | 256 |

| 11.4.7. BBoot 編集                        |     |

| 11.4.8. アプリケーション生成                              | 266 |

|-------------------------------------------------|-----|

| 11.4.9. プログラムファイル作成                             | 266 |

| 11.4.10. コンフィギュレーション                            |     |

| 11.5. スロットマシン完成                                 | 267 |

| 11.5.1. スロットマシン動作確認                             | 267 |

| 11.6. ソフトウェアのデバッグ                               |     |

| 11.6.1. ソフトウェアデバッグ用に FPGA プロジェクトを更新             |     |

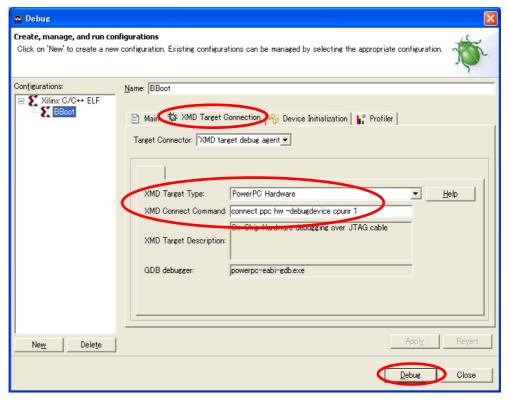

| 11.6.2. デバッガの設定                                 | 273 |

| 11.6.3. XMD の起動                                 | 276 |

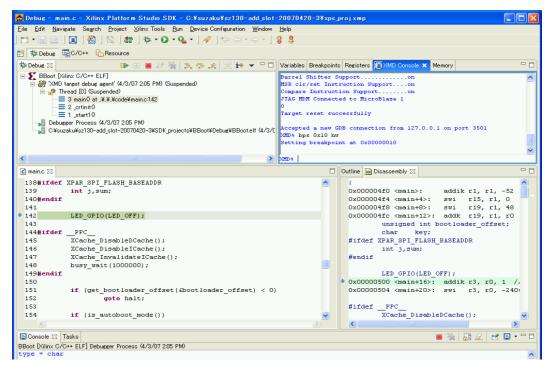

| 11.6.4. GDB を起動し、ソフトウェアのスタートをさせる                | 278 |

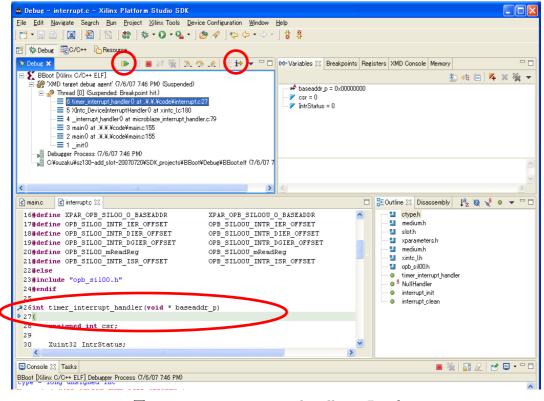

| 11.6.5. ステップ実行で割り込みの流れをみる                       |     |

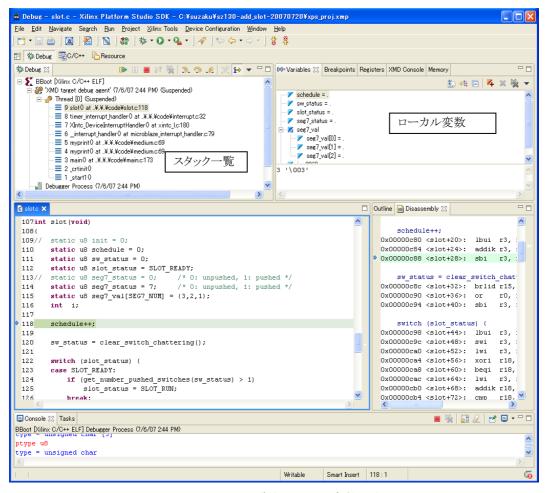

| 11.6.6. slot.c の動作を確認してみる                       | 282 |

| 12. こんなこともやってみよう                                | 283 |

| 12.1. EDK を ISE のサブモジュールとして読み込む                 | 283 |

| 12.1.1. EDK で作業                                 | 284 |

| 12.1.2. EDK から ISE へ移行                          | 286 |

| 12.1.3. ISE で作業                                 |     |

| 12.2. IP コア(ハード版)                               | 291 |

| 12.3. CGI で 7 セグメント LED をコントロール                 | 296 |

| 12.3.1. 7seg-led-control.c                      |     |

| 12.4. SDK を使ってデバッグ                              | 301 |

| 12.5. これから先は・・・                                 | 310 |

| 12.6. 最新版のダウンロード                                | 310 |

| 13. SUZAKU+LED/SW ボードのピンアサイン                    | 311 |

| 13.1. SUZAKU のピンアサイン                            | 311 |

| 13.1.1. SUZAKU CON1 RS-232C                     | 311 |

| 13.1.2. SUZAKU CON2 外部 I/O、フラッシュメモリ用コネクタ        | 312 |

| 13.1.3. SUZAKU CON3 外部 I/O コネクタ                 | 313 |

| 13.1.4. SUZAKU CON4 外部 I/O コネクタ                 | 314 |

| 13.1.5. SUZAKU CON5 外部 I/O コネクタ                 | 314 |

| 13.1.6. SUZAKU CON6 電源入力+3.3V                   | 315 |

| 13.1.7. SUZAKU CON7 FPGA JTAG 用コネクタ             | 315 |

| 13.1.8. SUZAKU D1,D3 LED                        | 315 |

| 13.1.9. SUZAKU JP1,JP2 設定用ジャンパ                  |     |

| 13.1.10. SUZAKU L2 Ethernet 10BASE-T/100BASE-TX |     |

| 13.2. LED/SW ボードのピンアサイン                         |     |

| 13.2.1. LED/SW CON1 テスト拡張用コネクタ                  |     |

| 13.2.2. LED/SW CON2 SUZAKU 接続コネクタ               |     |

| 13.2.3. LED/SW CON3 SUZAKU 接続コネクタ               |     |

| 13.2.4. LED/SW CON4 テスト拡張用コネクタ                  |     |

| 13.2.5. LED/SW CON6 +5V 入力コネクタ                  | 319 |

| 13.2.6. LED/SW CON7 RS-232C コネクタ                | 320 |

| 13.2.7. LED/SW 7 セグメント LED セレクタ                 |     |

| 13.2.8. LED/SW LED1~3 7 セグメント LED               |     |

| 13.2.9. LED/SW D1~4 単色 LED(緑)                   |     |

| 13.2.10. LED/SW SW1~3 押しボタンスイッチ                 |     |

| 13.2.11. LED/SW SW4 ロータリコードスイッチ                 | 322 |

| 14                                              | 292 |

### 表目次

|       | OTHER TITLE OF THE                         |     |

|-------|--------------------------------------------|-----|

|       | 1 SUZAKU の仕様                               |     |

|       | 2 SZ010、SZ030 のメモリマップ                      |     |

|       | 3 SZ130 のメモリマップ                            |     |

|       | 4 SZ310 のメモリマップ                            |     |

|       | 5 SZ410 のメモリマップ                            |     |

|       | 1 クロック、リセット信号 ピンアサイン                       |     |

| 表 2-2 | 2 機能用ピンアサイン(CON2)                          | 20  |

| 表 3-1 | 1 SUZAKU のコネクタ配置                           | 22  |

| 表 3-2 | 2 LED/SW のコネクタ配置                           | 22  |

| 表 5-1 | 1 ジャンパの設定と起動時の動作                           | 28  |

| 表 5-2 | 2 SUZAKU 初期設定時のユーザとパスワード                   | 36  |

|       | 1 フラッシュメモリマップ(SZ130 Flash:8MB)             |     |

|       | 2 フラッシュメモリマップ (SZ010:4MB)                  |     |

|       | 3 フラッシュメモリマップ (SZ030, SZ310:8MB)           |     |

|       | 4 フラッシュメモリマップ (SZ410:8MB)                  |     |

|       | 5 SUZAKU の書き換えかた                           |     |

|       | 1 FPGA 入力、出力                               |     |

|       | 1 FFGA 入力、出力                               |     |

|       |                                            |     |

|       | 3 ピンアサイン                                   |     |

|       | 1 ライブラリとパッケージ                              |     |

|       | 2 入出力方向                                    |     |

|       | 3 データタイプ                                   |     |

|       | 4 not、and、or のピンアサイン                       |     |

|       | 1 単色 LED 順次点灯ピンアサイン                        |     |

|       | 2 ロータリコードスイッチ(正論理)                         |     |

|       | 3 7セグメント LED デコーダ(正論理)                     |     |

| 表 9-4 | 4 7セグメント LED デコーダ ピンアサイン                   | 137 |

| 表 10  | -1 入力できるクロック周波数                            | 160 |

| 表 10  | -2 ピンアサイン(system.ucf)                      | 162 |

|       | -3 GPIO メモリアドレス                            |     |

|       | -4 nLE pin<0> ピンアサイン                       |     |

|       | -5 ピンアサイン                                  |     |

|       | -6 UART メモリアドレス                            |     |

|       | -7 OPB Clock Frequency                     |     |

|       | -8 CONSOLE ピンアサイン                          |     |

|       | -1 sil00u メモリアドレス                          |     |

|       | -2 自作 IPコア ピンアサイン                          |     |

|       | -1 シリアルコンソールの設定                            |     |

|       | -1 タリアルコンノールの最近<br>-2 SUZAKU CON1 RS-232C  |     |

|       |                                            |     |

|       | -3 SUZAKU CON2 外部 I/O、フラッシュメモリ用コネクタ        |     |

|       | -4 SUZAKU CON3 外部 I/O コネクタ                 |     |

|       | -5 SUZAKU CON4 外部 I/O コネクタ                 |     |

|       | -6 SUZAKU CON5 外部 I/O コネクタ                 |     |

|       | -7 SUZAKU CON7 FPGA JTAG 用コネクタ             |     |

|       | -8 SUZAKU D1, D3 LED                       |     |

|       | -9 SUZAKU JP1、JP2 設定用ジャンパ                  |     |

|       | -10 SUZAKU L2 Ethernet 10BASE-T/100BASE-TX |     |

| 表 13  | -11 LED/SW CON2 SUZAKU 接続コネクタ              | 317 |

| 表 | 13-12 | LED/SW CON3 SUZAKU 接続コネクタ     | 318 |

|---|-------|-------------------------------|-----|

| 表 | 13-13 | LED/SW CON4 フラッシュメモリ書き込み用コネクタ | 319 |

| 表 | 13-14 | LED/SW CON6 +5V 入力コネクタ        | 319 |

| 表 | 13-15 | LED/SW CON7 RS-232C コネクタ      | 320 |

| 表 | 13-16 | LED/SW 7セグメント LED セレクタ        | 320 |

| 表 | 13-17 | LED/SW LED1~3 7 セグメント LED     | 321 |

| 表 | 13-18 | LED/SW D1~4 単色 LED(緑)         | 321 |

| 表 | 13-19 | LED/SW SW1~3                  | 322 |

| 表 | 13-20 | LED/SW SW4                    | 322 |

### 図目次

| 図 1-1 SUZAKU とは                                                  | 1                  |

|------------------------------------------------------------------|--------------------|

| 図 1-2 MicroBlaze ブロック図 ····································      |                    |

| 図 1-3 SZ010, SZ030 の全体ブロック図                                      |                    |

| 図 1-4 SZ010, SZ030 のバス                                           |                    |

| 図 1-5 SZ010, SZ030 の主要部品配置図                                      |                    |

| 図 1-6 SZ130 の全体ブロック図 ····································        |                    |

|                                                                  |                    |

| 図 1-7 SZ130のバス ····································              |                    |

| 図 1-8 SZ130の主要部品配直図                                              |                    |

| 図 1-10 SZ310の主体プロック図                                             |                    |

| 図 1-10 SZ310の八人                                                  |                    |

| 図 1-11 SZ310の主要部品配直図                                             |                    |

| 図 1-12 SZ410の全体プロック図                                             |                    |

|                                                                  |                    |

| 図 1-14 SZ410 の主要部品配置図 ····································       |                    |

| 図 2-1 LED/SW 回路図(縮小版) ····································       |                    |

| 図 3-1 各種インターフェースの配置                                              |                    |

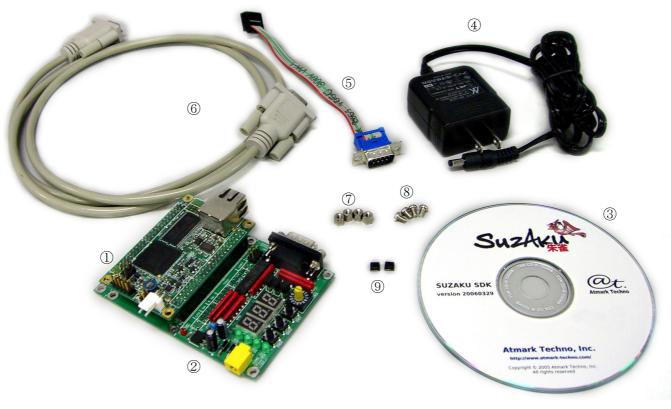

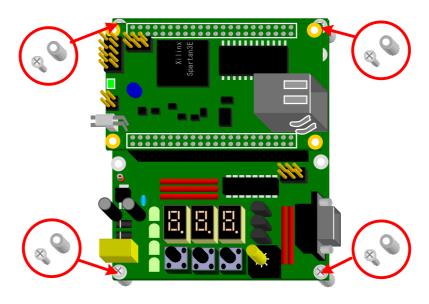

| 図 4-1 SUZAKU スターターキット(SZ130) ·····                               |                    |

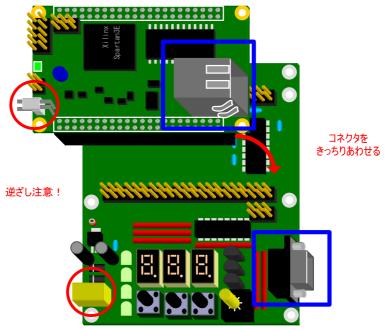

| 図 4-2 SUZAKUとLED/SW ボード接続                                        |                    |

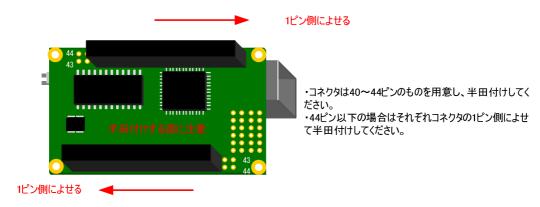

| 図 4-3 コネクタの半田付け                                                  |                    |

| 図 4-4 スペーサ取り付け                                                   |                    |

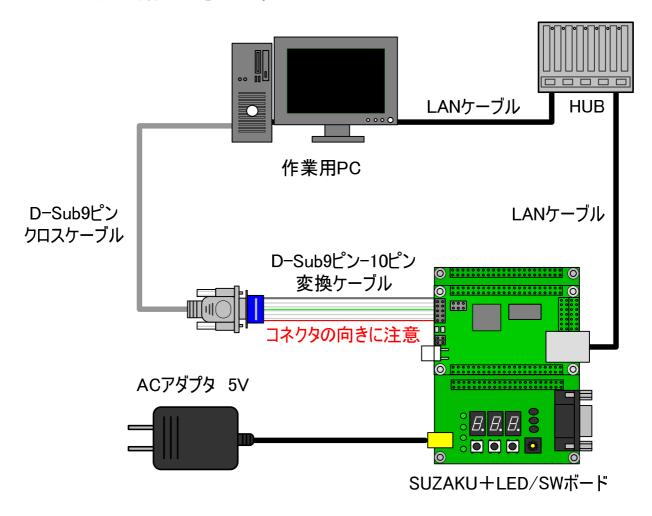

| 図 5-1 SUZAKU+LED/SW ボード配線 ······                                 |                    |

| 図 5-2 シリアルポート(Tera Term)の設定 ·····                                |                    |

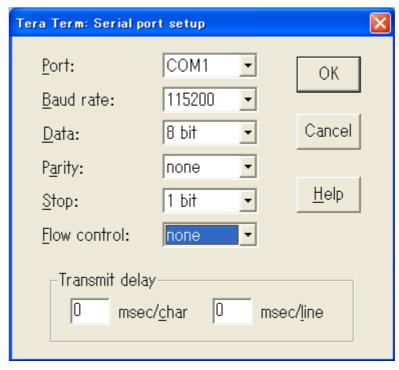

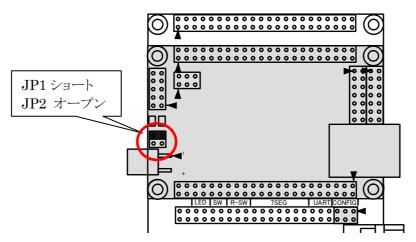

| 図 5-3 ブートローダモード ジャンパの設定                                          |                    |

| 図 5-4 電源系統                                                       |                    |

| 図 5-5 電源ケーブル接続の諸注意                                               |                    |

| 図 5-6 スロットマシンの起動                                                 | 32                 |

| 図 5-7 スロットマシンを動かしてみよう                                            | 33                 |

| 図 5-8 オートブートモード ジャンパの設定                                          | 33                 |

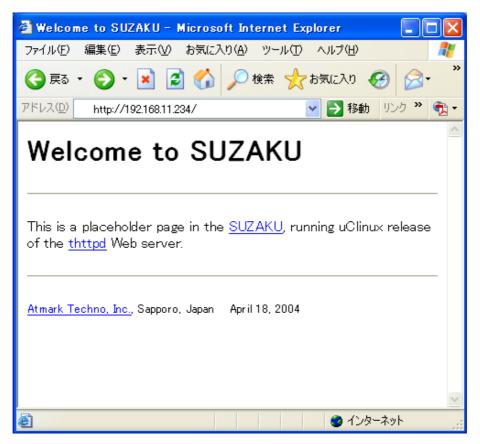

| ⊠ 5-9 SUZAKU Web Page ·····                                      | 37                 |

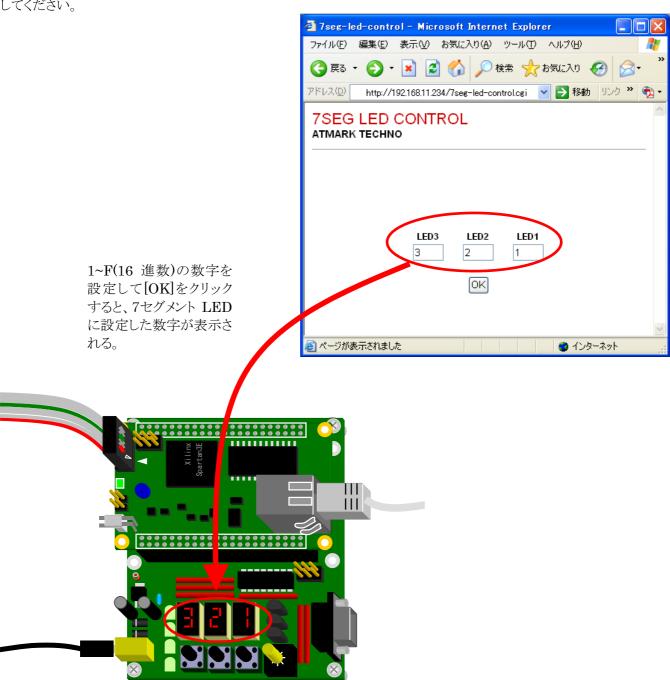

| 図 5-10 CGI を動かしてみる ····································          | 38                 |

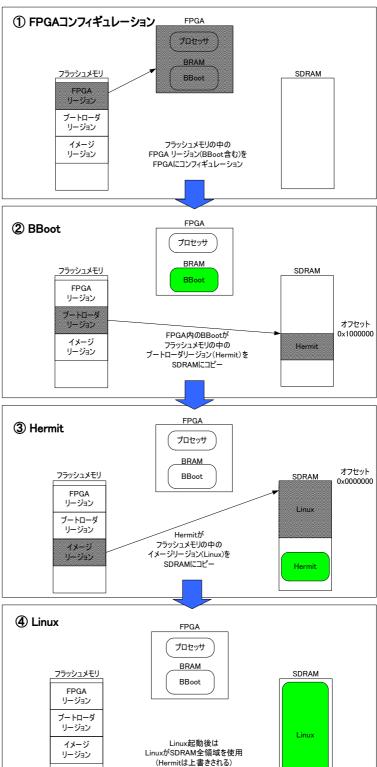

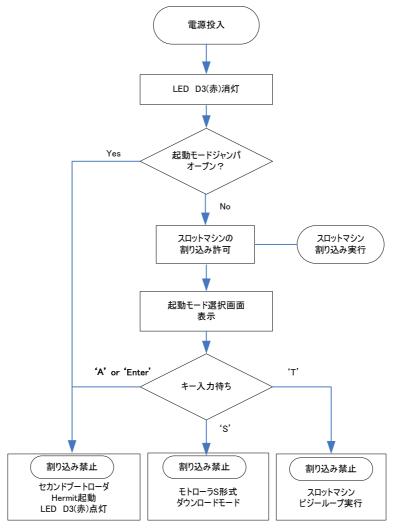

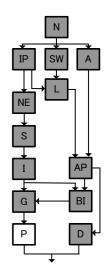

| 図 5-11 2 段階ブート                                                   | 39                 |

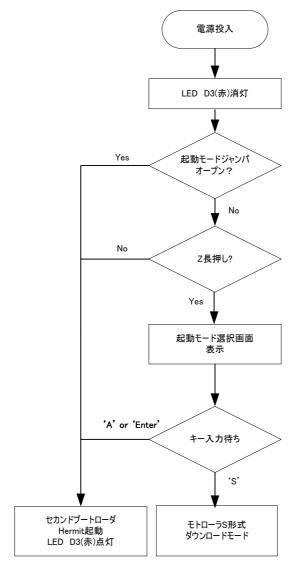

| 図 5-12 スターターキットの BBoot のフロー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  | 40                 |

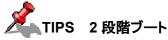

| 図 6-1 FPGA の書き込み                                                 |                    |

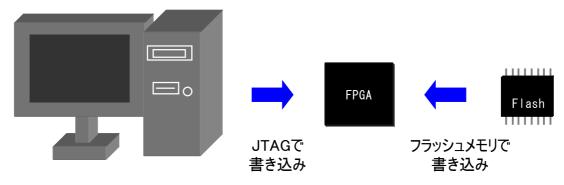

| 図 6-2 iMPACT 書き込み準備 ······                                       | 46                 |

| 図 6-3 iMPACT 起動 ···································              |                    |

| 図 6-4 iMPACT 設定画面 ····································           |                    |

| 図 6-5 FPGA デバイス発見(SZ130 の場合)                                     |                    |

| 図 6-6 bit ファイル選択 ····································            | 48                 |

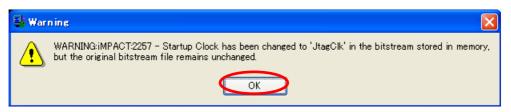

| ☑ 6-7 WARNING:iMPACT:2257 ···································    |                    |

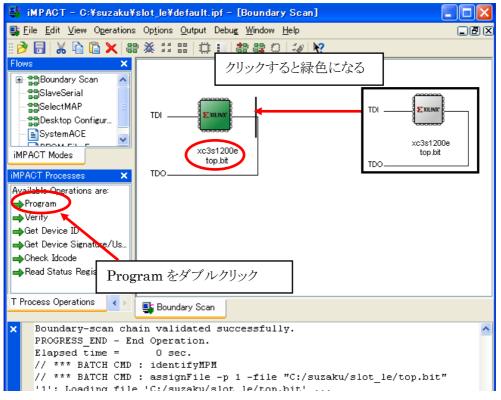

| 図 6-8 デバイス選択 ····································                |                    |

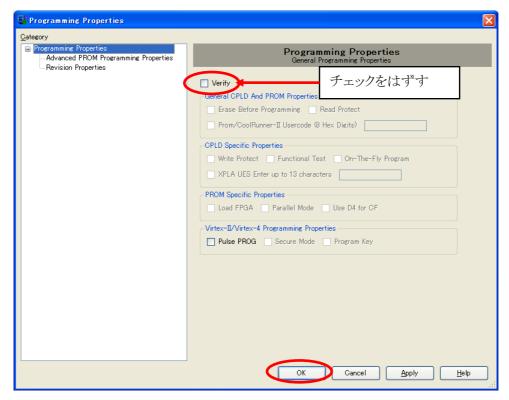

| 図 6-9 Program 設定 ···································             |                    |

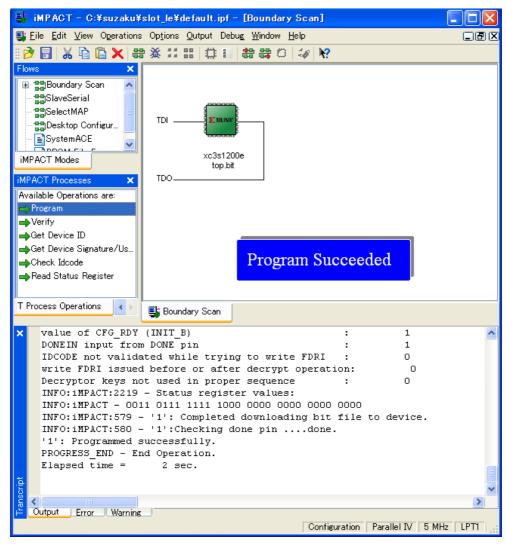

| 図 6·10 コンフィギュレーションデータ書き込み成功 ···································· |                    |

| 図 6-11 TE7720 の書き込み ····································         |                    |

| 図 6-12 LBplayer2 書き込み準備                                          |                    |

| 図 6-12 Lbptayer2 書き込み準備                                          |                    |

| 図 6-14 TE7720 iMPACT 立ち上げ                                        |                    |

| 図 6-14 TE7720 iMPACT 立ら上げ                                        |                    |

| 図 6-15 TET720 IMPACT 設定                                          |                    |

| 凶 b*10 fKUM 炒悪択                                                  | $\cdots \cdots 54$ |

| 义 |      | 'TE7720 確認画面 ······                                       |                  |

|---|------|-----------------------------------------------------------|------------------|

| 义 |      | 3 TE7720 デバイスファイル追加 ····································  |                  |

| 义 |      | TE7720 bit ファイルを開く ····································   |                  |

| 义 |      | ・TE7720 デバイスファイルさらに追加 ·······                             |                  |

| 义 |      | TE7720 準備完了 ····································          |                  |

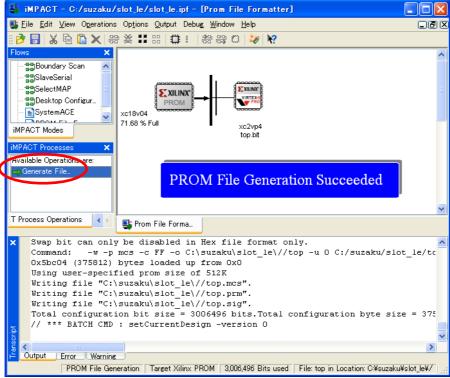

| 义 |      | 2 mcs ファイル出来上がり                                           |                  |

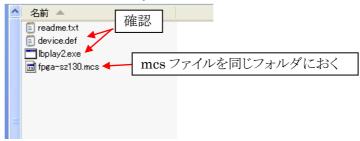

| 义 |      | mcsファイルコピー ······                                         |                  |

| 义 |      | LBPlay2 実行 ·····                                          |                  |

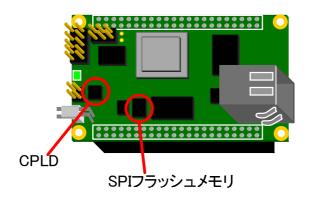

| 义 |      | 5 SZ130 の SPI フラッシュメモリの所在                                 |                  |

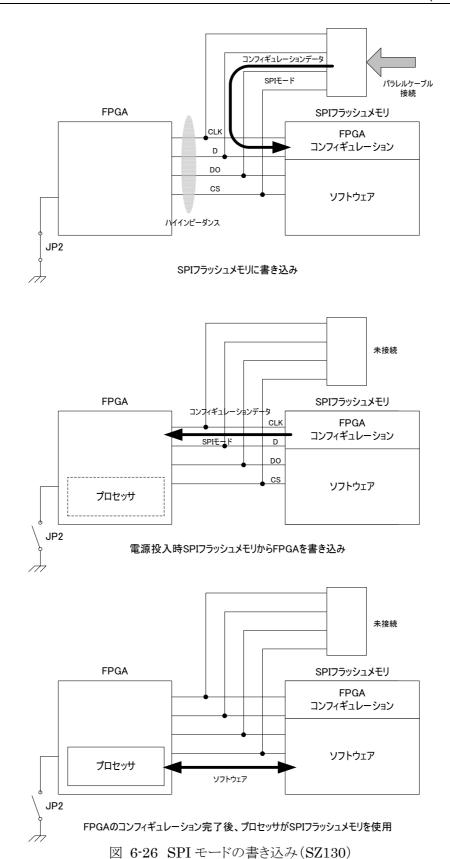

| 义 |      | 3 SPI モードの書き込み (SZ130)                                    |                  |

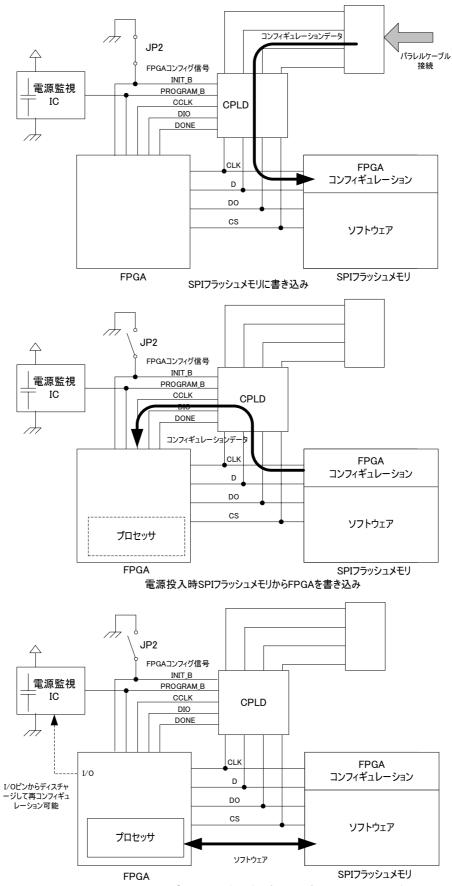

| 义 |      | ′SZ410の CPLD および SPI フラッシュメモリの所在                          |                  |

| 义 |      | 3 CPLD による書き込み(SZ410)                                     |                  |

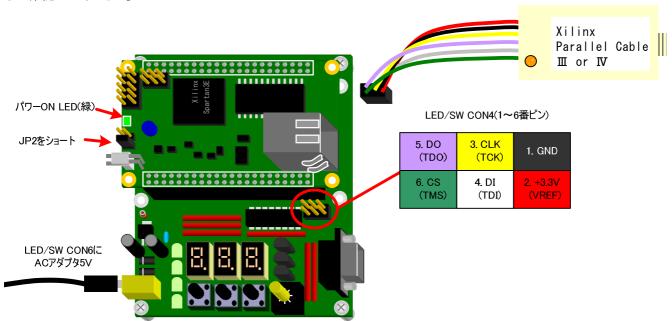

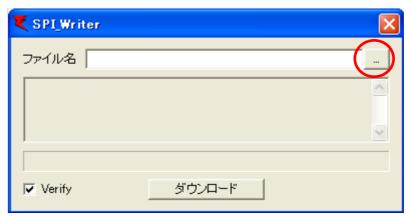

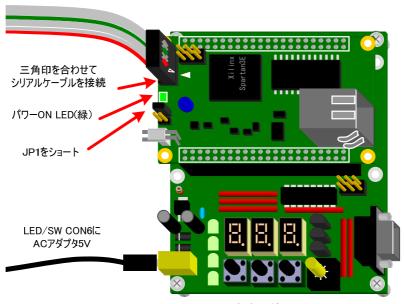

| 义 |      | SPI Writer 書き込み準備                                         |                  |

| 义 |      | SPI_Writer ·····                                          |                  |

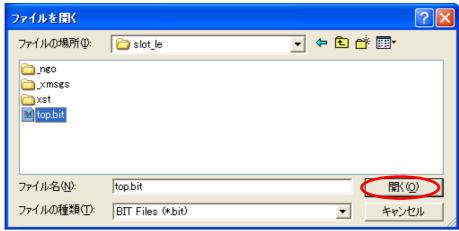

| 义 |      | bit ファイル選択 ····································           |                  |

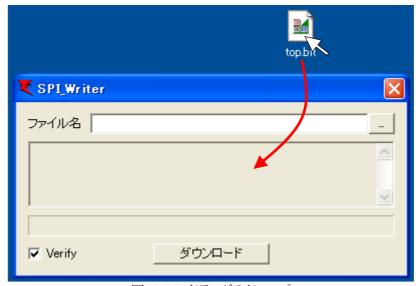

| 义 |      | ! ドラッグ&ドロップ                                               |                  |

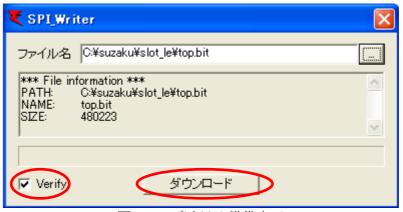

| 义 |      | : 書き込み準備完了                                                |                  |

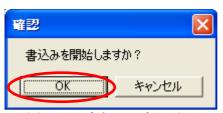

| 义 | 6-34 | . 書き込み確認画面                                                | 69               |

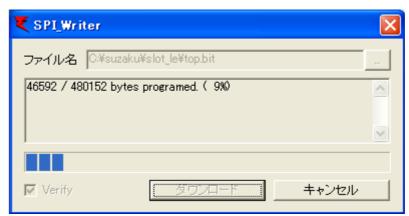

| 义 | 6-35 | i 書き込み中 ······                                            |                  |

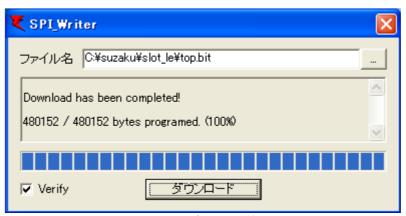

| 义 | 6-36 | ; 書き込み終了                                                  | 69               |

| 义 | 6-37 |                                                           |                  |

| 义 | 6-38 | 3 モトローラ S 形式書き換え準備 ······                                 | $\cdot \cdot 72$ |

| 义 | 6-39 | )srec ファイルを送る ·····                                       | 73               |

| 义 |      | )srec ファイル書き込み中 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      |                  |

| 义 |      | Linux 書き換え準備 ····································         |                  |

| 义 | 6-42 | ・シリアルポートを切断                                               | 76               |

| 义 | 6-43 | B Download 画面 ······                                      | 76               |

| 义 |      | - 書き込み進捗ダイアログ                                             |                  |

| 义 | 6-45 | う 書き込み終了                                                  | $\cdot \cdot 77$ |

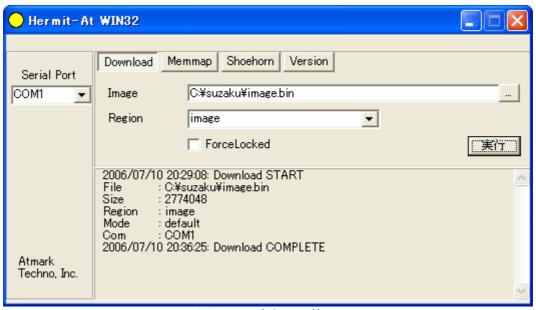

| 义 | 7-1  | 本書での ISE 開発フロー ······                                     | 79               |

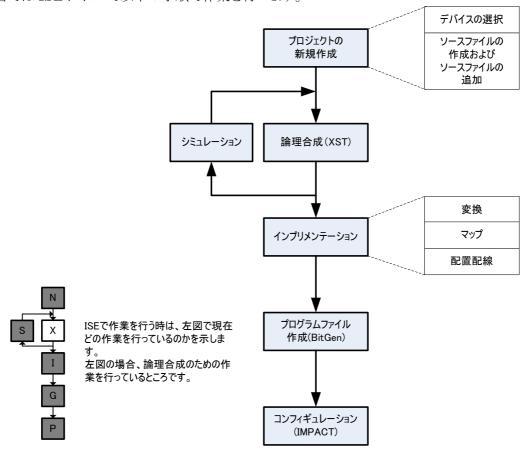

| 义 | 7-2  | 単色 LED 周辺回路 ······                                        | 80               |

| 义 | 7-3  | Project Navigator 起動 ·····                                | 81               |

| 义 | 7-4  | プロジェクトの新規作成                                               | 81               |

| 义 | 7-5  | デバイスの選択(SZ130 の場合) ····································   | 82               |

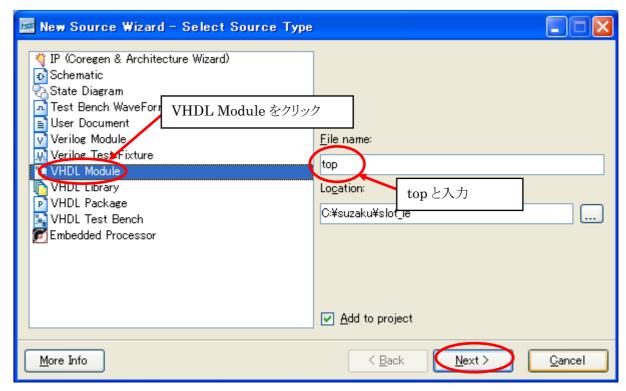

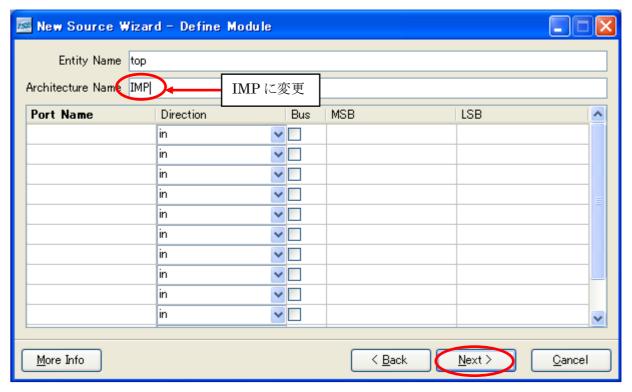

| 义 |      | New Source 作成·····                                        |                  |

| 义 | 7-7  | VHDL ソースファイル作成                                            | 83               |

| 义 |      | アーキテクチャ名定義                                                |                  |

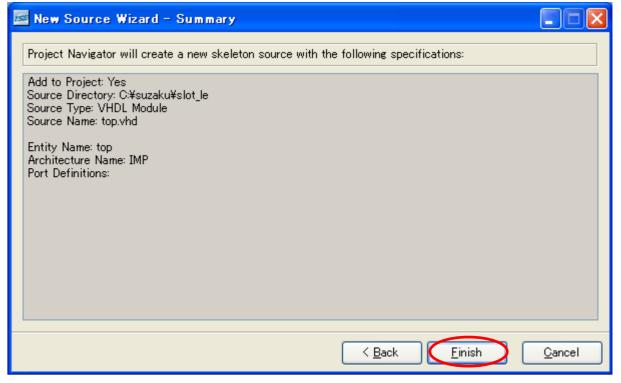

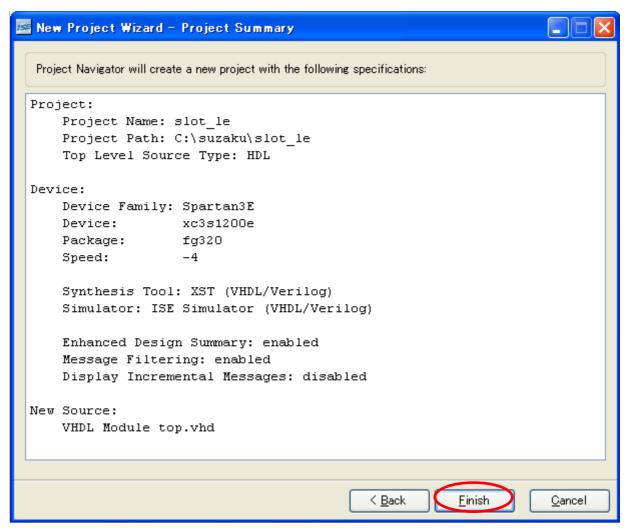

| 义 | 7-9  | ソースファイル作成確認画面                                             | 84               |

| 図 | 7-10 | ・ 最終確認画面(SZ130 の場合) · · · · · · · · · · · · · · · · · · · | 85               |

| 义 | 7-11 | 新規プロジェクト、ソースファイルのテンプレート作成完了                               | 86               |

| 义 | 7-12 | ソースコード入力                                                  | 87               |

| 図 | 7-13 | ; 文法チェック ······                                           | 88               |

|   |      | PACE を立ち上げる ······                                        |                  |

|   |      | i ucf ファイル作成確認 ····································       |                  |

| 図 |      | 3 PACE によるピンアサイン(SZ130 の場合)                               |                  |

| 図 |      | / ピンアサインのソースコード(SZ130 の場合) ·····                          |                  |

|   | 7-18 | ・ インプリメント・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             | 93               |

| 図 |      | ) bit ファイル作成 ····································         |                  |

| 図 |      | iMPACT 立ち上げ ····································          |                  |

|   |      | 空きピン処理の設定画面の出し方                                           |                  |

|   |      | · 空きピン処理設定····································            |                  |

| 义  | 7-23 | 少し光る理由                                                           | 98   |

|----|------|------------------------------------------------------------------|------|

|    |      | to を使って定義 ······                                                 |      |

| 义  | 8-2  | 押しボタンスイッチ周辺回路                                                    | 104  |

| 义  |      | not 回路と真理値表                                                      |      |

| 図  |      | and 回路と真理値表                                                      |      |

| 図  |      | or 回路と真理値表                                                       |      |

| 図  |      | 順序回路の概念図                                                         |      |

| 図  |      | D-FF の動作 ······                                                  |      |

| 図  | 8-8  | テストベンチ作成                                                         | ·111 |

| 図  | 8-9  | クロック波形作成                                                         | 112  |

| 図  |      | リセット波形生成                                                         |      |

| 図  |      | シミュレーション設定                                                       |      |

| 図  |      | シミュレーション結果・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   |      |

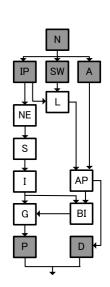

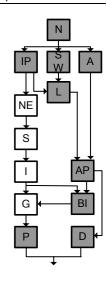

| 図  |      | スロットマシンの構成                                                       |      |

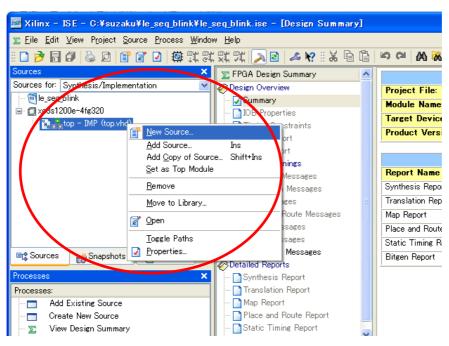

| 図  |      | New Source の追加・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・               |      |

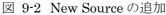

| 図  |      | New Source 名前入力 ······                                           |      |

|    |      | 既存のソースファイル追加                                                     |      |

|    |      | 既存のソースファイル追加時の確認・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             |      |

| 図  | 9-6  | 上位階層に設定・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      |      |

| 図  | 9-7  | 上位階層選択 · · · · · · · · · · · · · · · · · · ·                     |      |

| 図  |      | 見たい信号を追加・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     |      |

|    |      |                                                                  |      |

| 図図 |      | エッジ検出回路 ····································                     |      |

| 図  |      | エッジ検出の波形・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     |      |

|    | 9-11 |                                                                  |      |

|    |      | bit 連結······                                                     |      |

|    |      | ・シフトレジスタの波形・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  |      |

| 図  | 9-14 | ピンアサインでひっくり返す ····································               | 128  |

| 1  |      | 単色 LED 順次点灯 ····································                 |      |

| 図  |      | CoreConnect のビットラベルと信号                                           |      |

| 図  |      | ロータリコードスイッチ周辺回路とピンアサイン · · · · · · · · · · · · · · · · · · ·     |      |

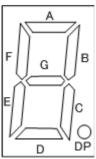

|    |      | セグメントの配置                                                         |      |

|    |      | 7 セグメント LED 周辺回路 ····································            |      |

|    | 9-20 |                                                                  |      |

|    |      | Pattern Wizard                                                   |      |

|    |      | Pattern Wizard · · · · · · · · · · · · · · · · · · ·             |      |

|    |      | デコーダシミュレーション結果                                                   |      |

|    |      | 7セグメント LED デコーダ ······                                           |      |

|    |      | 7 セグメント LED ダイナミック点灯                                             |      |

| 図  | 9-26 | ダイナミック点灯シミュレーション結果                                               | 142  |

|    |      | ダイナミック点灯                                                         |      |

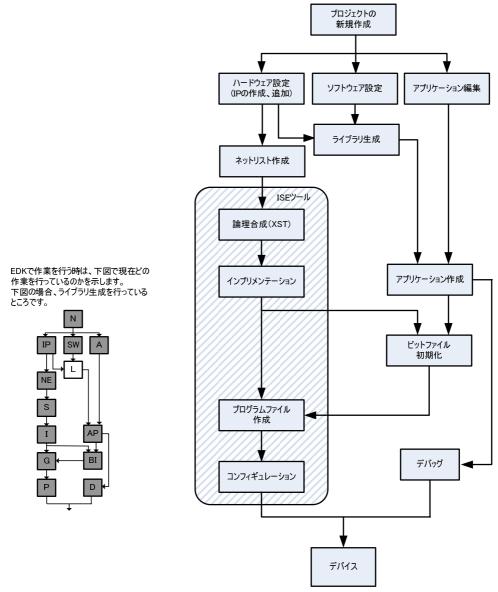

|    |      | 本書での EDK 開発フロー ······                                            |      |

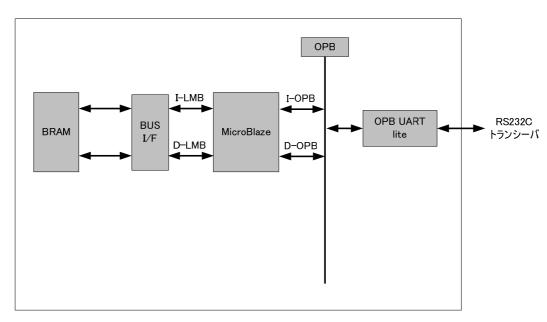

|    |      | Hello SUZAKU プロジェクト(MicroBlaze) ······                           |      |

|    |      | Hello SUZAKU プロジェクト(PowerPC)・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |      |

|    |      | BSB 選択 ·····                                                     |      |

|    |      | BSB ファイル保存                                                       |      |

|    |      | 新しいデザインをはじめる                                                     |      |

|    |      | ターゲットボードの選択                                                      |      |

|    |      | FPGA とプロセッサの設定 ·····                                             |      |

|    |      | MicroBlaze の設定                                                   |      |

|    |      | 0 PowerPC の設定                                                    |      |

| 义  | 10-1 | 1 I/O デバイスの選択                                                    | 151  |

| 义 | 10-12 | I/O デバイスの選択追加 ·······                                             | 152 |

|---|-------|-------------------------------------------------------------------|-----|

| 义 | 10-13 | 周辺回路の選択追加・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     | 153 |

| 図 |       | ソフトウェアに関する設定                                                      |     |

| 図 | 10-15 | 設定の確認(MicroBlaze) ······                                          | 155 |

| 义 | 10-16 | 設定の確認(PowerPC)・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 156 |

| 义 |       | システムの生成完了                                                         |     |

| 図 | 10-18 | XPS に戻る ·····                                                     | 158 |

| 図 | 10-19 | XPS の表示 ·····                                                     | 158 |

| 図 |       | DCM の変更・・・・・・                                                     |     |

| 図 |       | DCM の一部 ·····                                                     |     |

|   |       | RS232 のピンを削除 ······                                               |     |

| 図 |       | SZ130 の場合のピンアサイン(system.ucf) ······                               |     |

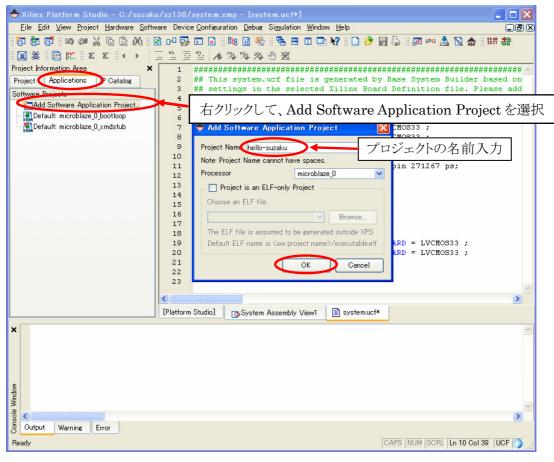

| 図 | 10-24 | hello-suzaku 作成······                                             | 163 |

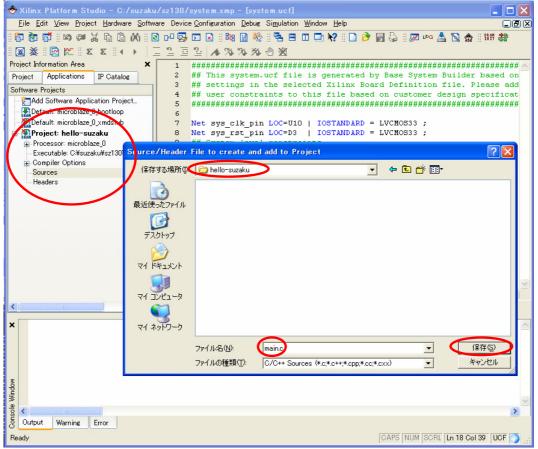

| 巡 |       | main.c 作成 ······                                                  |     |

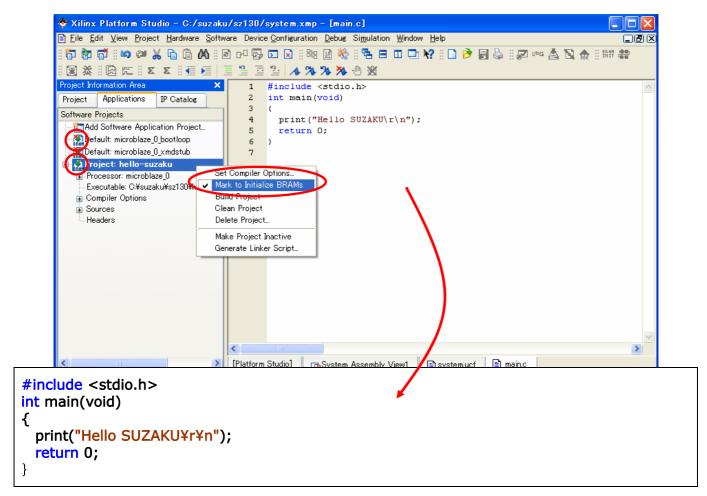

|   |       | Hello SUZAKU のソースコード(main.c) ···································· |     |

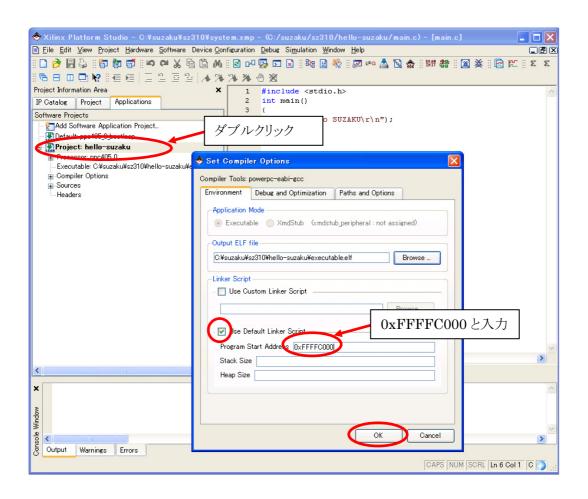

| 図 | 10-27 | リンカースクリプトの設定(PowerPC)                                             | 166 |

|   | 10-28 | bit ファイル作成 ····································                   | 167 |

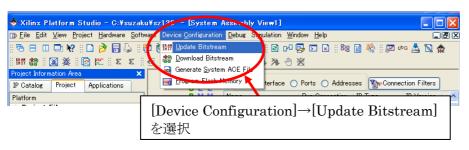

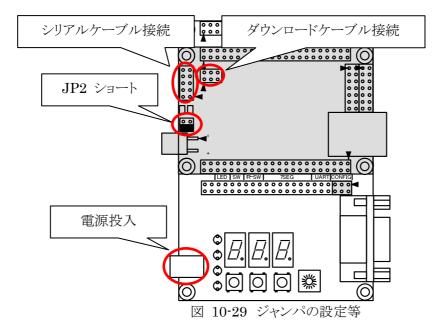

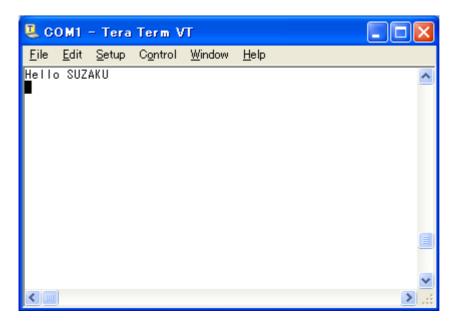

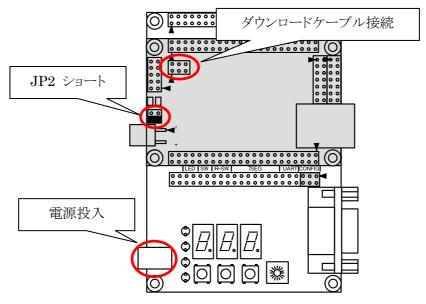

| 図 | 10-29 | ジャンパの設定等                                                          | 167 |

| 図 |       | 書き込み成功例・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                       |     |

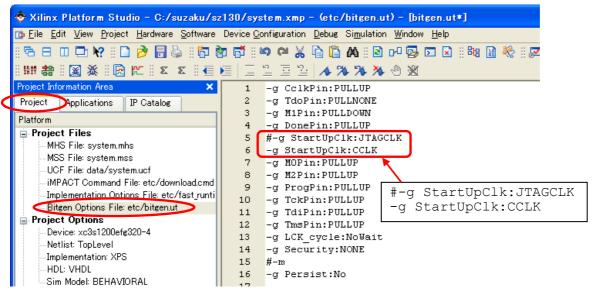

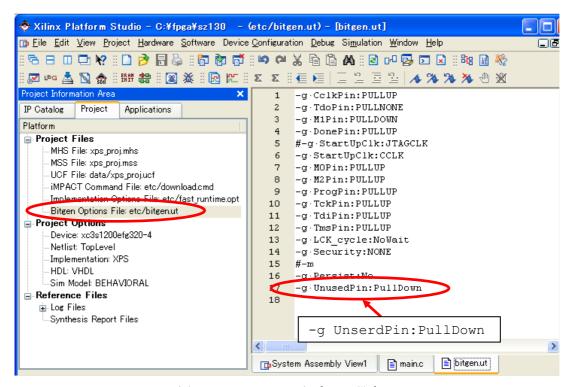

| 図 |       | bitgen.ut の変更 ···································                 |     |

| 図 |       | XPS 起動······                                                      |     |

| 図 |       | SZ010、SZ030 のデフォルト(EDK)                                           |     |

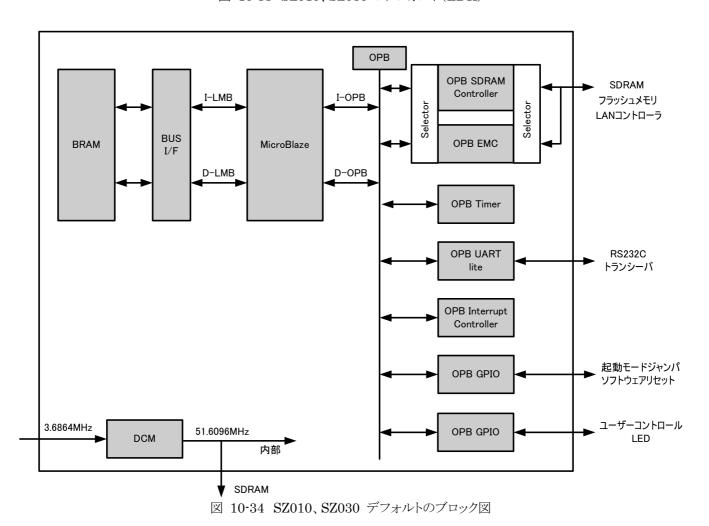

| 図 |       | SZ010、SZ030 デフォルトのブロック図                                           |     |

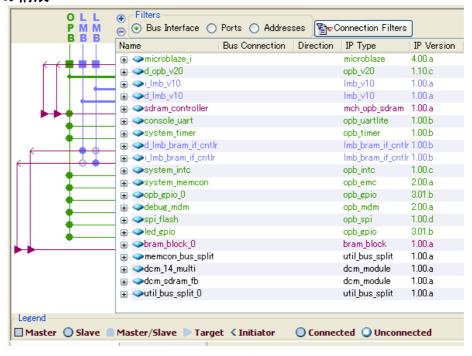

|   |       | SZ130 のデフォルト(EDK)                                                 |     |

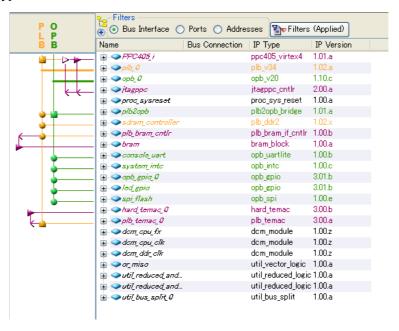

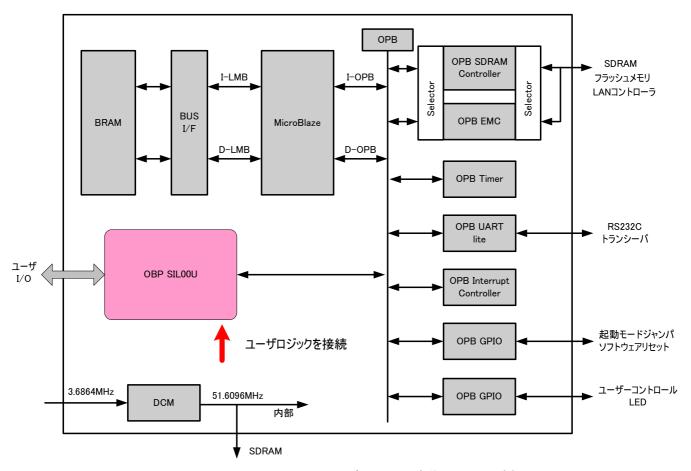

| 図 | 10-36 | <b>SZ130</b> デフォルトのブロック図                                          | 171 |

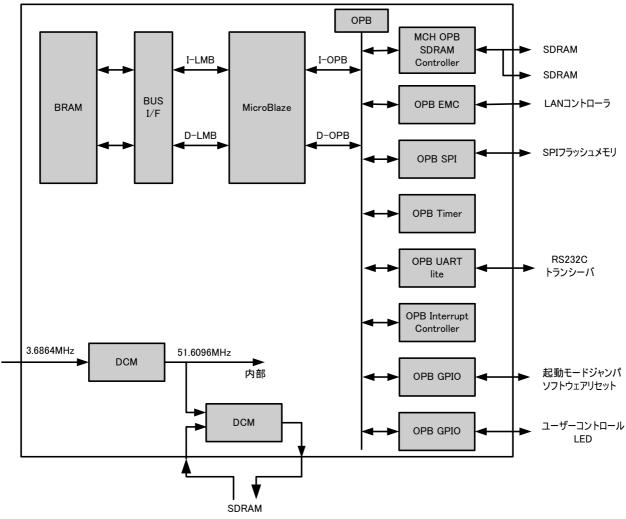

|   |       | SZ310 のデフォルト(EDK)                                                 |     |

| 図 |       | SZ310 デフォルトのブロック図                                                 |     |

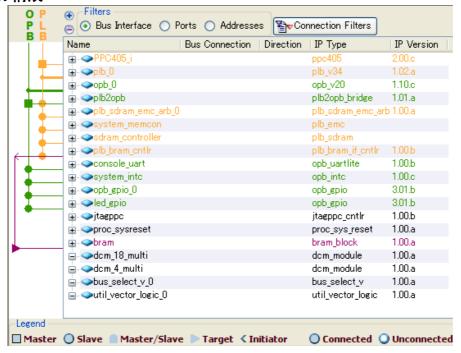

| 図 |       | SZ410 のデフォルト(EDK)                                                 |     |

| 図 | 10-40 | SZ410 デフォルトのブロック図                                                 | 173 |

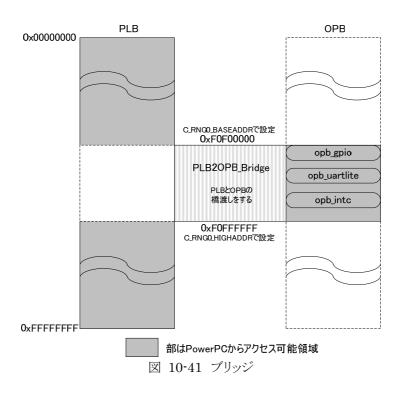

| 図 | 10-41 | ブリッジ                                                              | 177 |

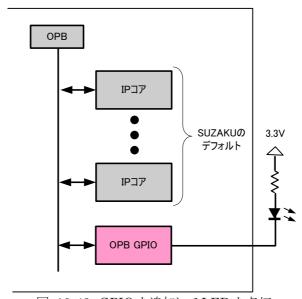

| 図 |       | GPIO を追加して LED を点灯 ······                                         |     |

|   |       | opb_gpio の追加 ···································                  |     |

|   |       | OPB バスに接続 ······                                                  |     |

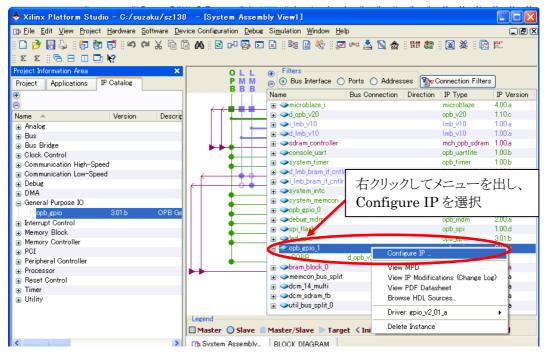

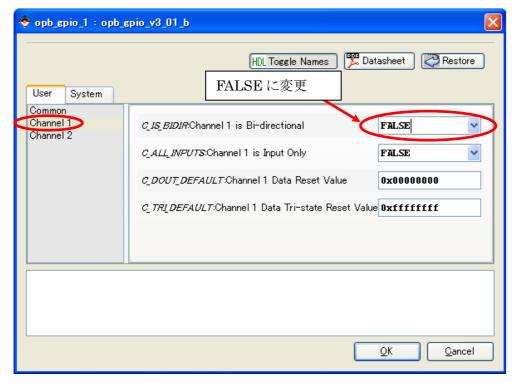

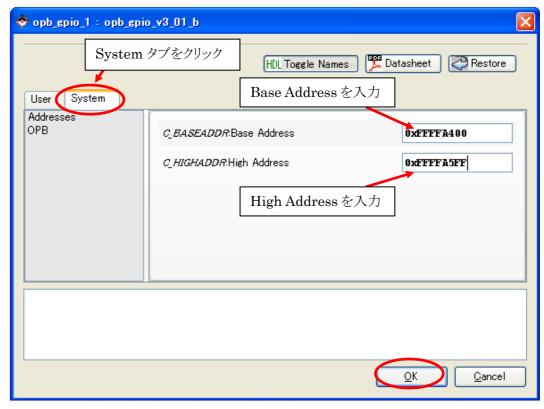

| 図 | 10-45 | Configure IP                                                      | 180 |

|   |       | バス幅の設定 ······                                                     |     |

|   |       | その他設定変更                                                           |     |

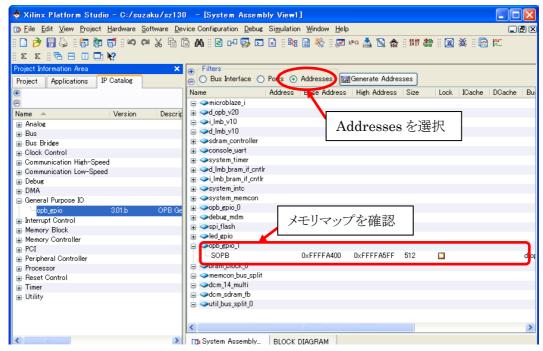

| 义 | 10-48 | メモリアドレス設定                                                         | 182 |

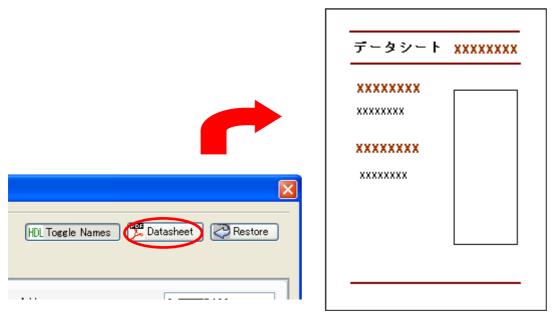

| 义 | 10-49 | データシートの出し方                                                        | 183 |

|   |       | メモリマップ確認                                                          |     |

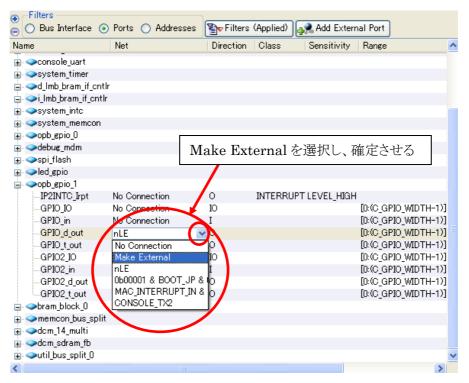

|   |       | Net 名入力 ······                                                    |     |

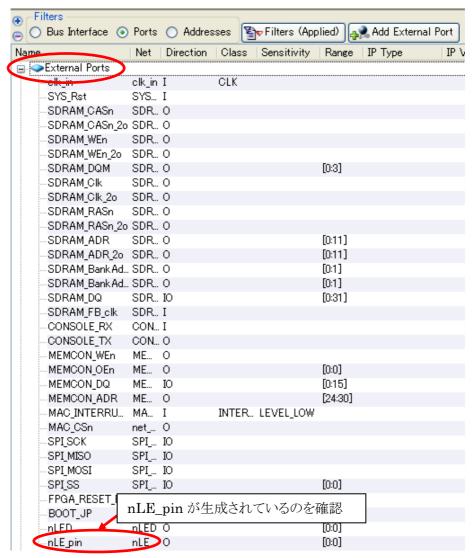

|   |       | 外部信号にする ······                                                    |     |

|   |       | 信号名変更                                                             |     |

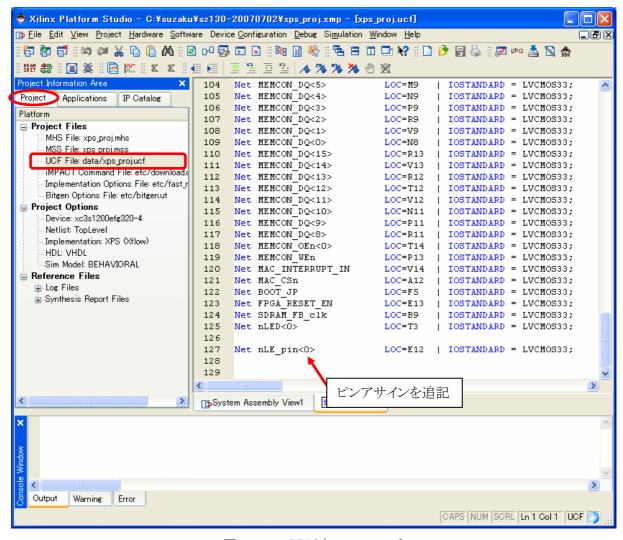

|   |       | GPIO(xps_proj.ucf) ·····                                          |     |

| 図 | 10-55 | ネットリスト作成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | 188 |

| 図 | 10-56 | bit ファイル (Hard) 作成 ···································            | 188 |

|   |       | GPIO Driver 設定                                                    |     |

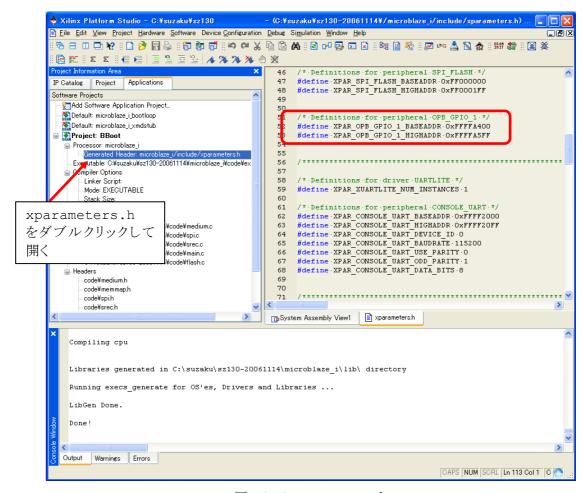

|   |       | xparameters.h ······                                              |     |

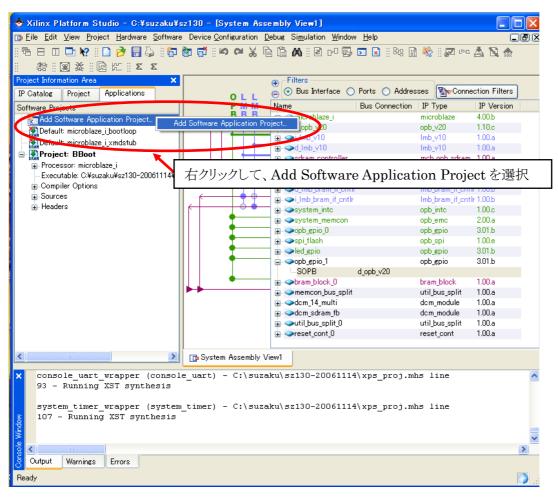

|   |       | アプリケーション作成                                                        |     |

|   |       | アプリケーションのプロジェクト名                                                  |     |

|   |       | New File 作成 ·····                                                 |     |

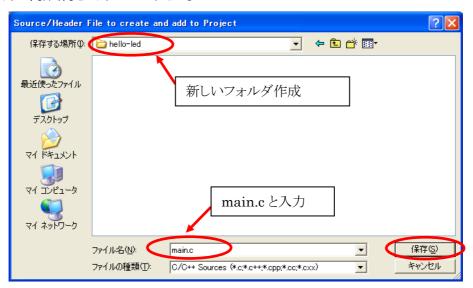

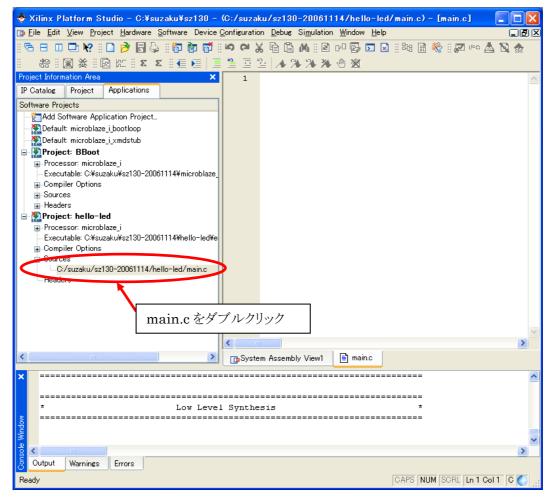

| 図 | 10-62 | main.c 作成 ·····                                                   | 193 |

| 义 |        | main.c を開く ·····                                                                                    |      |

|---|--------|-----------------------------------------------------------------------------------------------------|------|

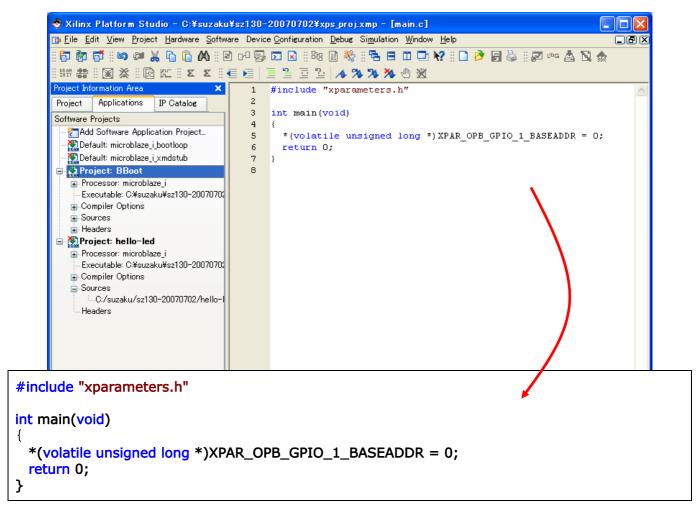

| 义 | 10-64  | 単色 LED 点灯のソースコード(main.c) ·······                                                                    | 194  |

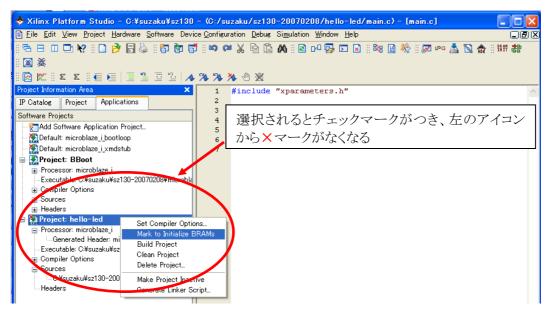

| 义 | 10-65  | hello-led を書き込むように設定 ······                                                                         | 195  |

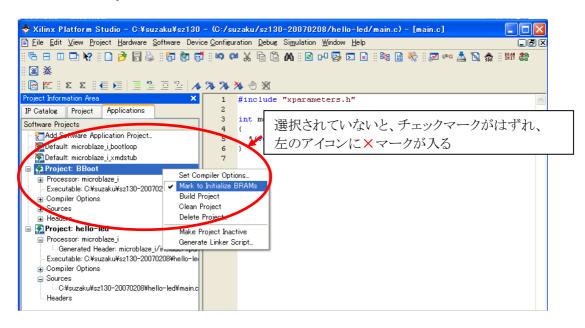

| 义 | 10-66  | BBoot は書き込まないように設定 ·····                                                                            | 195  |

| 义 | 10-67  | リンカースクリプト設定                                                                                         | 196  |

| 义 | 10-68  | スタートアドレス設定                                                                                          | 196  |

| 図 | 10-69  | elf ファイル作成 ······                                                                                   | 197  |

| 义 | 10-70  | bit ファイル作成 ······                                                                                   | 197  |

| 义 |        | ジャンパの設定等                                                                                            |      |

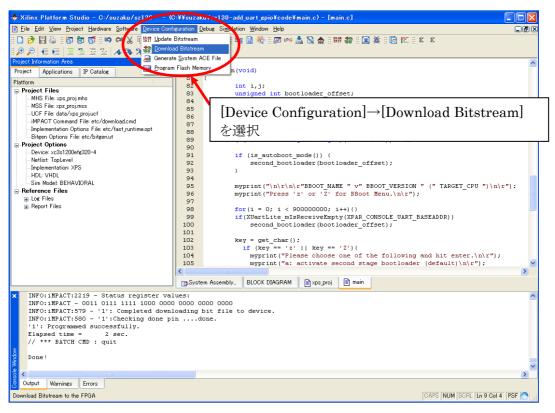

| 义 | 10-72  | コンフィギュレーション                                                                                         | 199  |

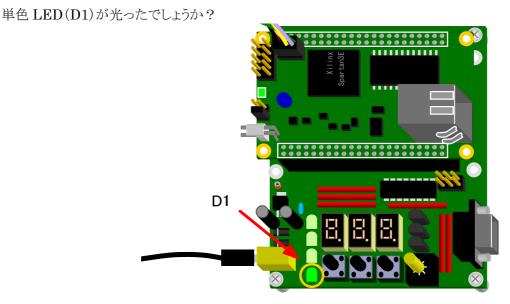

| 义 | 10-73  | 単色 LED(D1)点灯 ·······                                                                                | 199  |

| 义 | 10-74  | Bitgen のオプション設定                                                                                     | 200  |

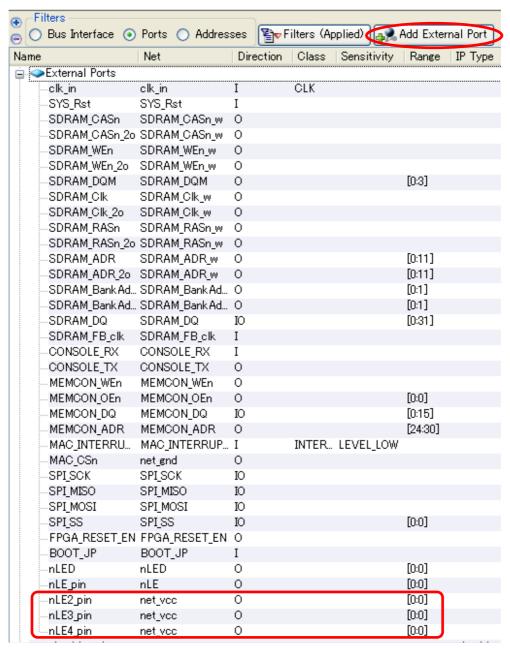

| 义 | 10-75  | EDK での空きピンの処理 ·····                                                                                 | 201  |

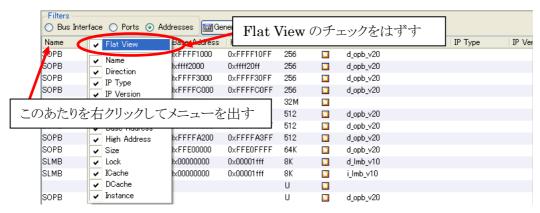

| 义 | 10-76  | Flat View ····                                                                                      | 202  |

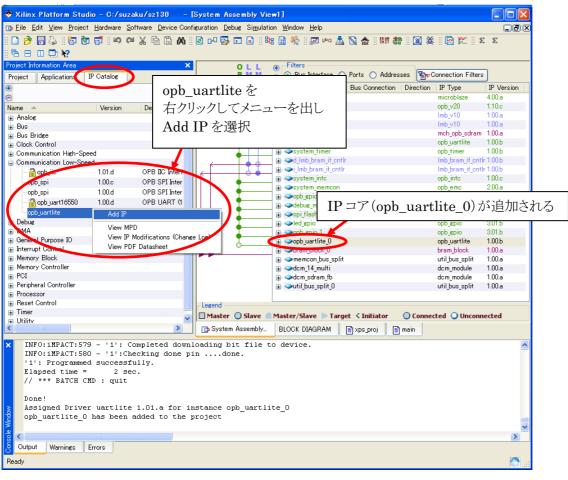

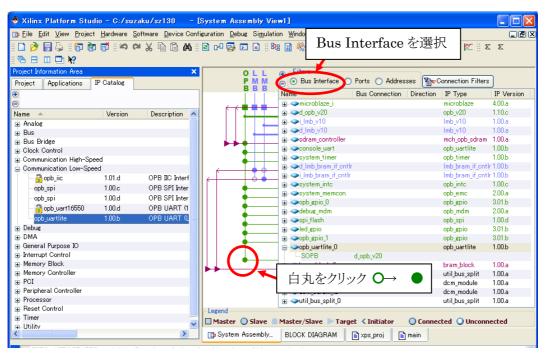

| 义 | 10-77  | opb_uartlite の追加 ······                                                                             | 203  |

| 义 |        | OPB バスに接続 ······                                                                                    |      |

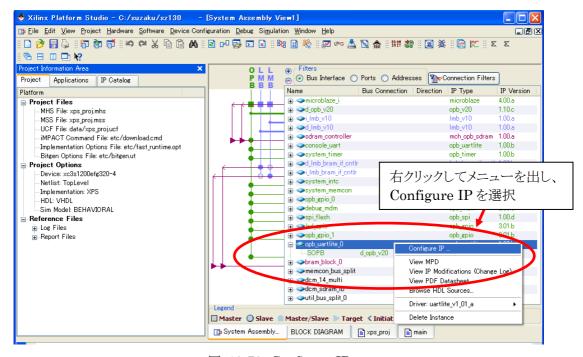

| 义 |        | Configure IP ·····                                                                                  |      |

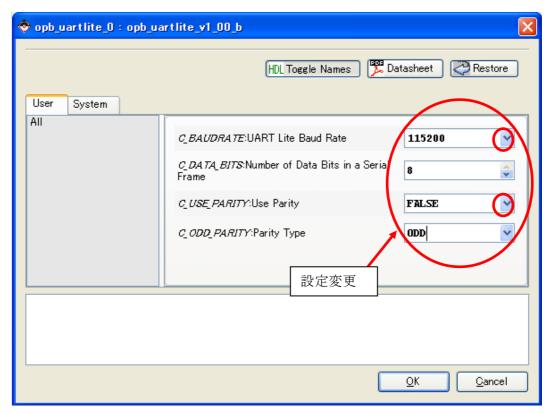

| 义 |        | UART 設定変更 ······                                                                                    |      |

| 义 |        | メモリアドレス設定                                                                                           |      |

| 义 |        | クロック周波数の設定                                                                                          |      |

| 义 |        | メモリマップ確認                                                                                            |      |

| 义 | 10-84  | 信号の定義                                                                                               | 209  |

| 义 |        | UART(xps_prj.ucf) ·····                                                                             |      |

| 义 |        | UART Driver 設定 ·····                                                                                |      |

| 义 |        | 送受信ソースコード追加(main.c) ····································                                            |      |

| 义 |        | bit ファイルの作成                                                                                         |      |

| 义 |        | ジャンパの設定等                                                                                            |      |

| 义 |        | シリアル通信 動作確認 ······                                                                                  |      |

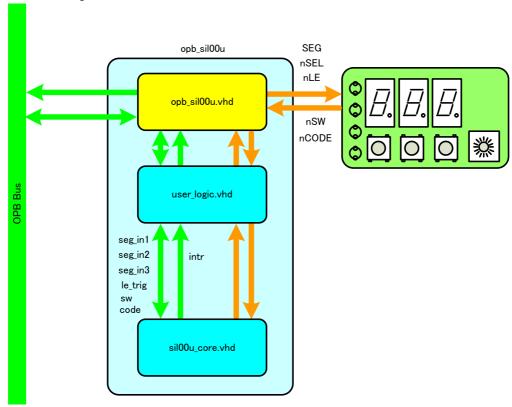

| 义 |        | スロットマシンへの道のり                                                                                        |      |

| 义 |        | 自作 IP コア ······                                                                                     |      |

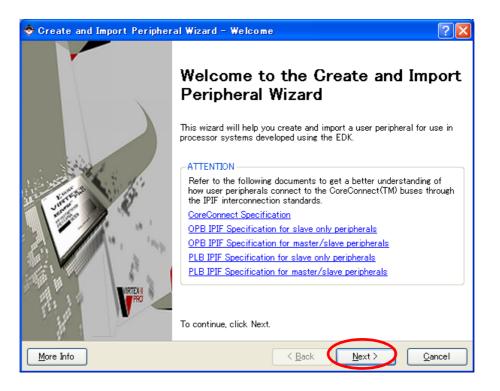

| 义 |        | Create and Import Peripheral Wizard の起動のさせ方                                                         |      |

| 义 | 11-4 ( | Create and Import Peripheral Wizard ······                                                          | 217  |

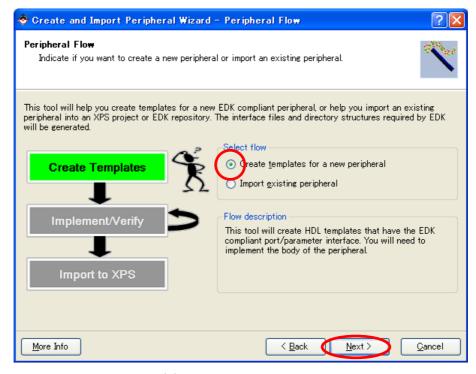

|   |        | Peripheral Flow ·····                                                                               |      |

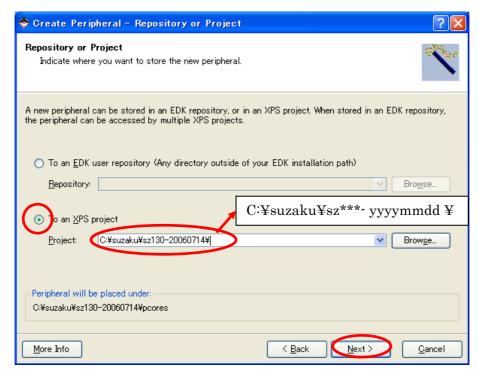

| 図 |        | コアの生成場所の指定                                                                                          |      |

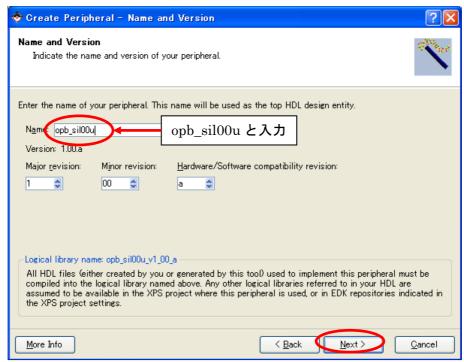

| 図 |        | コアの名前                                                                                               |      |

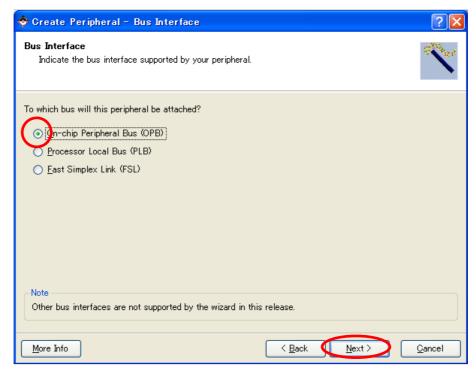

|   |        | ベスの選択                                                                                               |      |

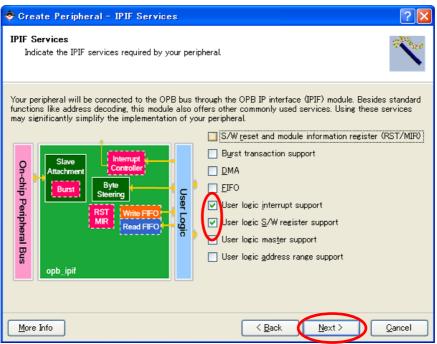

| 凶 |        | テンプレート追加                                                                                            |      |

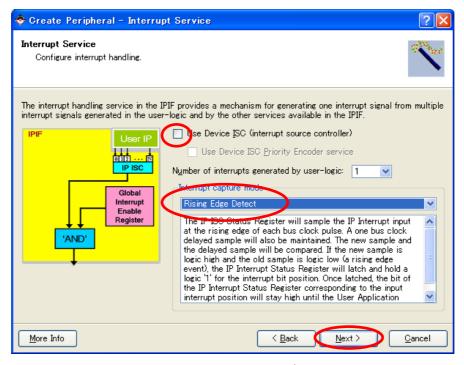

| 巡 |        | Interrupt 設定 ······                                                                                 |      |

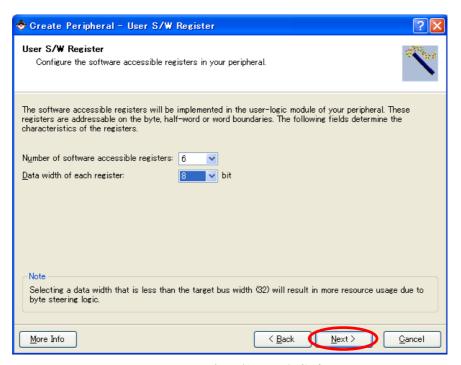

| 凶 |        | レジスタ数とバス幅指定・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                     |      |

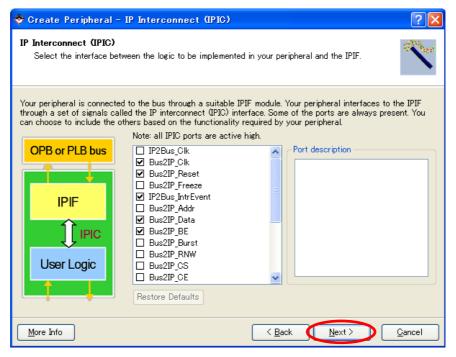

| 凶 |        | IPIC 設定 ·····                                                                                       |      |

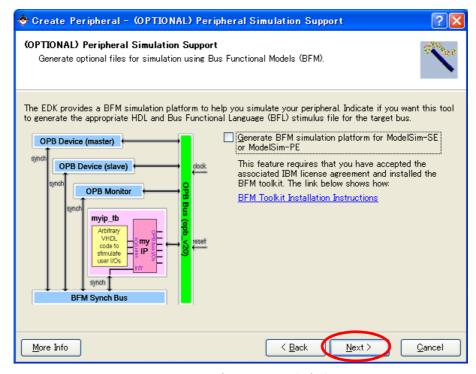

| 凶 |        | サポートファイル生成確認・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                    |      |

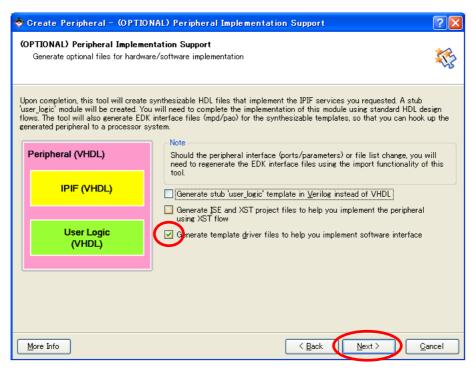

| 図 |        | オプション設定                                                                                             |      |

| 凶 |        | 終了······                                                                                            |      |

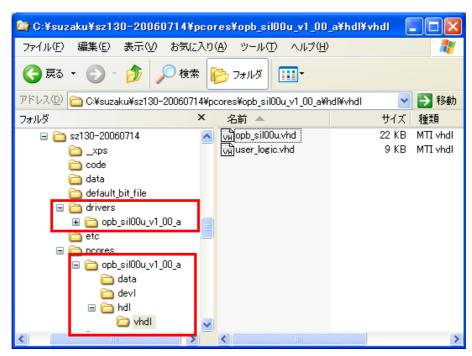

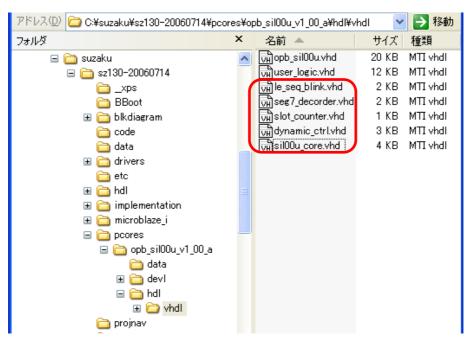

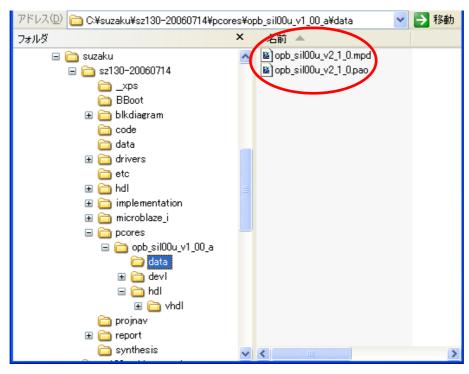

| 図 |        | フォルダ構成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                          |      |

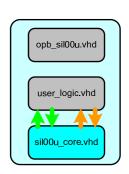

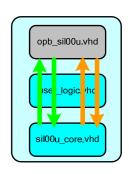

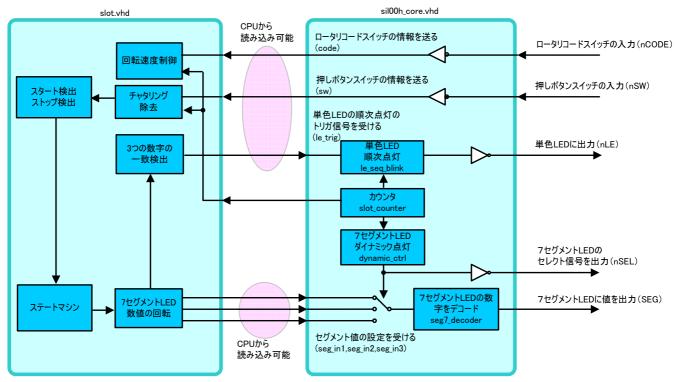

| 図 |        | 自作 IP コア(ソフト版)の仕様                                                                                   |      |

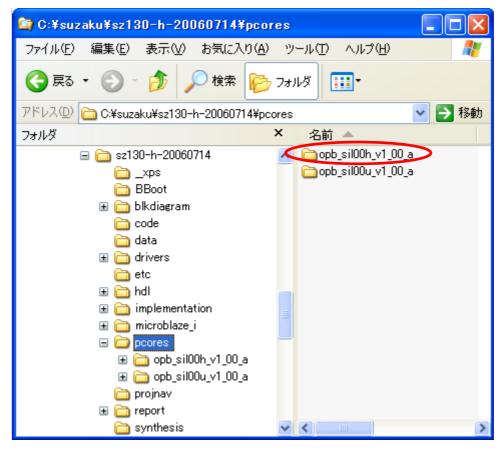

| 図 |        | コアをコピー ······· フォルダ構成 ······                                                                        |      |

| 図 |        |                                                                                                     |      |

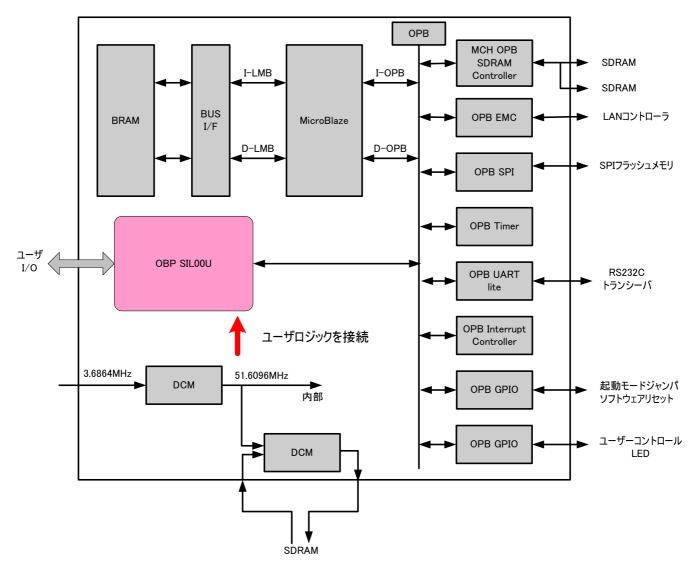

| 図 |        | SZ010、SZ030 のデフォルトに自作 IP コアを追加 ·······SZ130 のデフォルトに自作 IP コアを追加 ···································· |      |

| 図 | 11-21  | SZ130 のテフォルトに目作 IP コアを追加                                                                            | 239  |

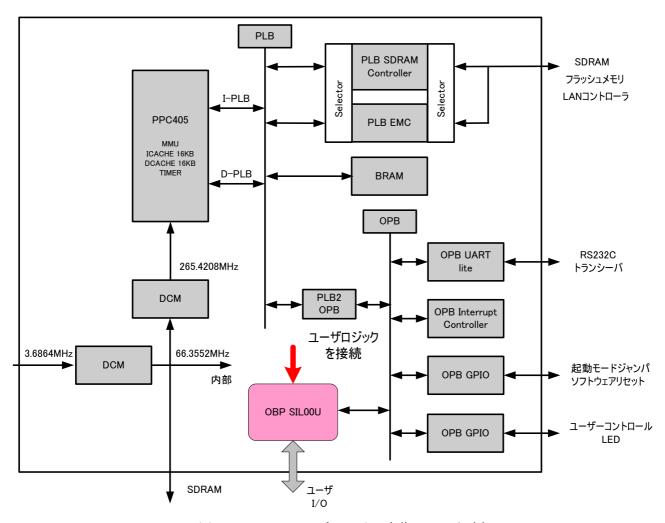

| 図 |        | SZ410 のデフォルトに自作 IP コアを追加                                                                            |      |

| 义 | 11-72  | <b>52410</b> v// /オ/レトルに日1ト 1 <b>F</b> ー/ を担加                                                       | 44 L |

| 义 | 11-24 | 自作 IP コア読み込み ······                                          | 242 |

|---|-------|--------------------------------------------------------------|-----|

| 図 | 11-25 | 自作 IP コア追加 ······                                            | 243 |

|   |       | OPB バスに接続 ······                                             |     |

| 义 | 11-27 | アドレス設定画面呼び出し                                                 | 244 |

| 図 | 11-28 | アドレス設定                                                       | 244 |

| 図 | 11-29 | メモリマップ確認                                                     |     |

| 図 | 11-30 | NET 名入力 ·····                                                | 246 |

| 义 | 11-31 | 外部信号にする ······                                               |     |

| 図 | 11-32 | 出力信号定義・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   | 248 |

| 义 | 11-33 | 残り出力信号定義                                                     | 249 |

| 义 | 11-34 | 割り込みコントローラ                                                   | 250 |

| 义 | 11-35 | 割り込み設定1                                                      | 251 |

| 义 | 11-36 | 割り込み設定 2                                                     | 252 |

| 义 | 11-37 | 割り込み設定 3                                                     | 252 |

| 义 | 11-38 | 割り込み設定 4                                                     |     |

| 义 | 11-39 | 自作 IP コア (xps_proj.ucf) ·····                                | 254 |

| 図 | 11-40 | エラーレポート                                                      | 256 |

| 义 | 11-41 | BBoot のフロー・・・・・                                              | 258 |

| 义 | 11-42 | BBoot の構成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 259 |

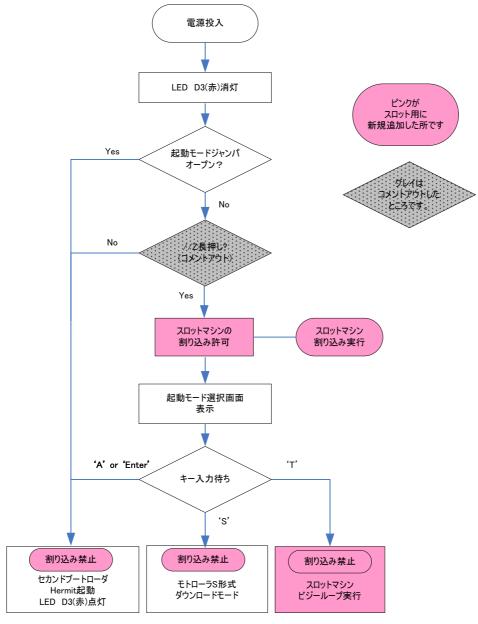

| 义 | 11-43 | スロットマシンのフロー                                                  | 260 |

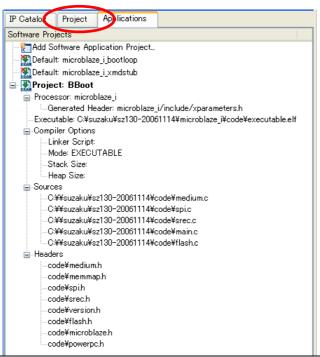

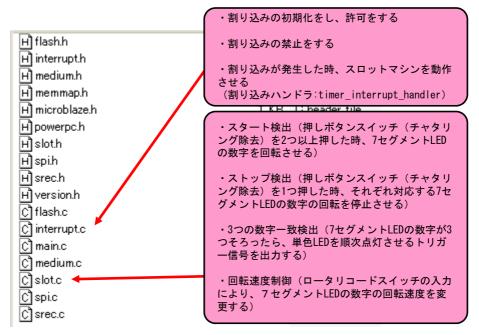

| 図 | 11-44 | ソースファイルコピー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・               | 261 |

| 义 | 11-45 | ソースファイル追加                                                    | 262 |

| 义 |       | ソースファイル選択                                                    |     |

| 义 |       | ヘッダファイル追加                                                    |     |

| 义 | 11-48 | ジャンパの設定等                                                     | 267 |

| 図 | 11-49 | スロットマシン実行画面 1                                                | 268 |

| 図 | 11-50 | スロットマシン完成                                                    | 268 |

| 义 | 11-51 | MicroBlaze のデバッグ設定                                           | 269 |

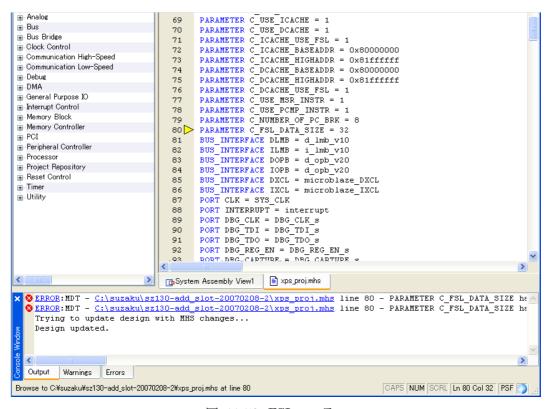

| 図 | 11-52 | FSL のエラー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 | 270 |

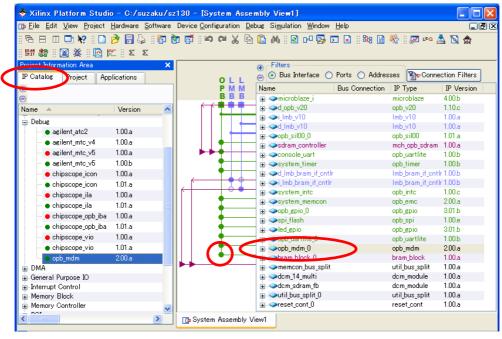

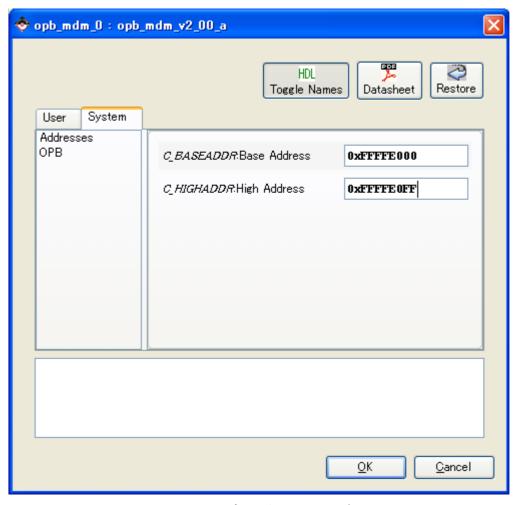

| 図 | 11-53 | opb-mdm を追加してバスに接続 ····································      | 270 |

| 図 |       | デバッガのアドレス設定                                                  |     |

| 図 | 11-55 | 8kByte → 16kByte に変更                                         | 272 |

|   |       | コンパイラオプション                                                   |     |

| 义 | 11-57 | デバッグオプション                                                    | 274 |

| 図 | 11-58 | XMD の接続 ······                                               | 276 |

| 义 | 11-59 | デバッグ設定                                                       | 278 |

| 図 | 11-60 | main で Break ······                                          | 278 |

| 図 | 11-61 | 0x10 で Break                                                 | 280 |

| 义 | 11-62 | _interrupt_handler()で Break ······                           | 280 |

| 义 |       | XIntc_DeviceInterruptHandler( )で Break ·······               |     |

| 义 | 11-64 | timer_interrupt_handler() ~ Break ······                     | 281 |

| 义 | 11-65 | slot() Teak                                                  | 282 |

|   |       | ローカル変数やスタックの一覧                                               |     |

|   |       | EDK SUZAKU のデフォルト・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        |     |

|   |       | [SE/EDK8.1i の場合のオプション設定                                      |     |

|   |       | xps_proj_stub.vhd をコピー · · · · · · · · · · · · · · · · · · · |     |

|   |       | Project Navigator 起動 ···································     |     |

|   |       | プロジェクトの新規作成                                                  |     |

|   |       | デバイスの選択(SZ130 の場合) ······                                    |     |

|   |       | ソースコード入力                                                     |     |

|   |       | IPコア(ハード版)の仕様 ······                                         |     |

| 図 |       | IP コア (ハード版) 追加 ······292                                          |

|---|-------|--------------------------------------------------------------------|

| 义 |       | IP コア(ハード版)追加確認292                                                 |

| 义 |       | MSS File 変更                                                        |

| 义 | 12-12 | MHS File 変更                                                        |

| 义 |       | IP コア (ハード版) に置き換え ······294                                       |

| 义 |       | 不要なファイルの削除294                                                      |

| 义 | 12-15 | main.c から割り込みの記述を削除 ······295                                      |

| 义 | 12-16 | · · · · · · · · · · · · · · · · · · ·                              |

| 义 | 12-17 |                                                                    |

| 义 | 12-18 | SDK 起動の際の注意 ·······301                                             |

| 义 | 12-19 | , , , , , , , , , , , , , , , , , , ,                              |

| 义 | 12-20 |                                                                    |

| 义 | 12-21 |                                                                    |

| 义 | 12-22 | - P                                                                |

| 义 | 12-23 | BBoot.elf 作成 ············304                                       |

| 义 |       | Program Hardware Setting · · · · · 304                             |

| 义 |       | コンフィギュレーションデータダウンロード・・・・・・・305                                     |

| 义 | 12-26 | BreakPoint 設定 ·······305                                           |

| 义 | 12-27 | , , , , , , , , , , , , , , , , , , ,                              |

| 义 |       | BBoot を追加 ·······306                                               |

| 义 |       | XMD の設定(Microblaze の場合) ····································       |

| 义 |       | XMD の設定(PowerPC の場合)                                               |

| 义 |       | main 関数で Break ····································                |

| 义 |       | $timer\_interrupt\_handler \ \colored{CBreak} \ \cdots \cdots 308$ |

| 义 |       | スタック一覧やローカル変数を確認309                                                |

| 义 |       | JTAG ピンアサイン315                                                     |

| 义 |       | フラッシュメモリ書き込み ピンアサイン319                                             |

| 义 |       | +5V センタープラスピン ······319                                            |

| 义 | 13-4  | 7 セグメント LED ···································                    |

### 例目次

| 例 5-1 SUZAKU の起動ログ(SZ130 の場合)                        | 34  |

|------------------------------------------------------|-----|

| 例 5-2 固定 IP アドレスの割り当て                                |     |

| 例 5-3 ネットワークの設定の表示                                   | 36  |

| 例 7-1 信号の記述を追記(top.vhd)                              | 99  |

| 例 8-1 VHDL 基本構造                                      | 100 |

| 例 8-2 entity 記述                                      | 101 |

| 例 8-3 信号の定義                                          | 101 |

| 例 8-4 architecture 記述                                | 102 |

| 例 8-5 内部信号定義                                         | 102 |

| 例 8-6 プロセス文                                          | 103 |

| 例 8-7 not 記述                                         | 104 |

| 例 8-8 and 記述                                         | 105 |

| 例 8-9 or 記述                                          | 105 |

| 例 8-10 not, and, or(top.vhd)                         | 106 |

| 例 8-11 カウンタ記述                                        |     |

| 例 8-12 クロックの立ち上がりエッジに同期                              |     |

| 例 8-13 同期リセット                                        |     |

| 例 8-14 if 文                                          |     |

| 例 8-15 other で初期化                                    |     |

| 例 8-16 カウンタ(slot_counter.vhd)                        |     |

| 例 8-17 generic 文                                     |     |

| 例 9-1 単色 LED 順次点灯(le_seq_blink.vhd)                  |     |

| 例 9-2 単色 LED 順次点灯(top.vhd)                           |     |

| 例 9-3 component 文                                    |     |

| 例 9-4 port map 文                                     |     |

| 例 9-5 エッジ検出                                          |     |

| 例 9-6 シフトレジスタ                                        |     |

| 例 9-7 bit 連結                                         |     |

| 例 9-8 7 セグメント LED デコーダ(seg7_decoder.vhd)             |     |

| 例 9-9 case 文                                         |     |

| 例 9-10 7 セグメント LED デコーダ (top.vhd)                    |     |

| 例 9-11 ダイナミック点灯(dynamic_ctrl.vhd)                    |     |

| 例 9-12 ダイナミック点灯(top.vhd)                             |     |

| 例 10-1 GPIO を追加した mhs ファイル                           |     |

| 例 10-2 GPIO の設定を追加した mss ファイル                        |     |

| 例 10-3 xparameters.h の定義の例                           |     |

| 例 10-4 xuartlite_l.h に定義されている関数                      |     |

| 例 11-1 コア(sil00u_core.vhd)                           |     |

| 例 11-2 sil00u(user_logic.vhd)                        |     |

| 例 11-3 sil00u(opb_sil00u.vhd)                        |     |

| 例 11-4 opb_sil00u_v2_1_0.mpd                         |     |

| 例 11-5 opb_sil00u_v2_1_0.pao                         |     |

| 例 11-6 opb_sil00u.c                                  |     |

| 例 11-7 自作 IP コア (main.c)                             |     |

| 例 11-8 XMD の起動ログ(SZ130 の場合)                          |     |

| 例 11-9 Breakpoint 設定(SZ010, SZ030, SZ130 の場合)        |     |

| 例 11-10 Breakpoint 設定(SZ310, SZ410 の場合)              |     |

| 例 12-1 CGI で 7 セグメント LED をコントロール(7seg-led-control.c) | 297 |

# 1.SUZAKU について

初めに"SUZAKU"がどのようなボードであるのか簡単に説明します。SUZAKU の詳細については本書内いたるところにちりばめられていますので、ここでは概要をつかんでください。

### 1.1. SUZAKU の特徴

SUZAKU(朱雀)は FPGA をベースとしたボードコンピュータです。 FPGA 上にプロセッサと周辺ペリフェラルコアを構成し、オペレーティングシステムとして Linux を採用しています。

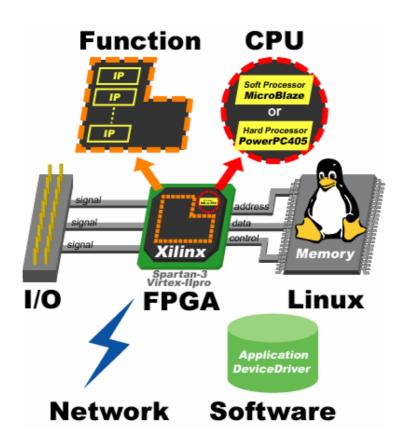

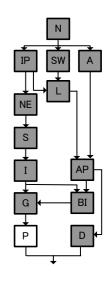

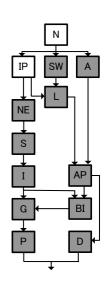

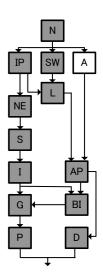

図 1-1 SUZAKUとは

### FPGA & Function

Xilinx の FPGA を採用し、大規模で柔軟な拡張をすることが出来ます。 SZ010、SZ030 は Spartan-3、SZ130 は Spartan-3E、SZ310 は Virtex-II Pro、SZ410 は Virtex-4 FX を搭載しています。 FPGA の内部は Xilinx やサードパーティ各社から供給される IP(Intellectual Property)を使用することで、必要な機能を容易に 追加することが出来ます。 また、ユーザによってもカスタマイズが可能です。

### CPU

SZ010、SZ030、SZ130 は低コストで資産継承性の高いソフトプロセッサの MicroBlaze を採用し、SZ310、SZ410 は高性能で実績の高いハードプロセッサの PowerPC を採用しています。

### Linux & Software

Linux を標準のオペレーティングシステムとして採用しているので、アプリケーションソフトウェアの開発には GNU のアセンブラや C コンパイラ等を使用することができます。 SZ010、SZ030、SZ130 は MMU 不要の  $\mu$  Clinux、SZ310、SZ410 は標準的な Linux に対応しています。 デバイスドライバから各種サーバソフトウェアまで、オープンソースで開発された Linux 対応の豊富なソフトウェア資産を活用することが出来ます。

### ● I/O

基板外周に SZ010、SZ030、SZ130、SZ410 は 86 ピン、SZ310 は 70 ピンのユーザが自由に使える外部 I/O を実装しています。例えば、GPIO や UART の数を増やし、外部 I/O ピンに割り当てるなどのカスタマイズが簡単に行えます。

### Network

ボードには LAN(10BASE-T/100BASE-TX)が実装されています。 LAN コントローラデバイスドライバ、各種プロトコルが最初から用意されているので、簡単にネットワークに接続できます。

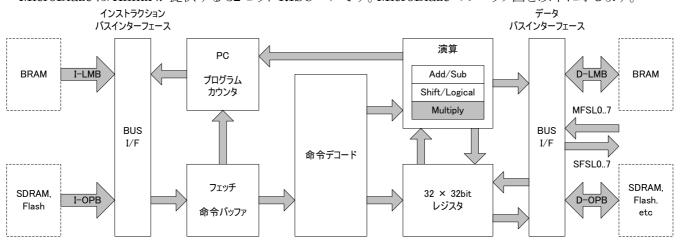

MicroBlaze は Xilinx が提供する 32 ビット RISC コアです。MicroBlaze のブロック図を以下に示します。

図 1-2 MicroBlaze ブロック図

### 主な機能

- ・32bitRISC プロセッサ

- ・32bit 固定長命令

- ・32 個の汎用 32bit レジスタ

- ・MMUなし

- ・命令キャッシュとデータキャッシュ

- ・ハードウェア乗算器

- ハードウェアデバッグロジック対応

- ・ペリフェラルバス OPB(CoreConnect)

# 1.2. 仕様

SUZAKU の主な仕様を以下に示します。

表 1-1 SUZAKU の仕様

|               | SUZAKU-S                      |            |                      | SUZAKU-V           |                 |  |

|---------------|-------------------------------|------------|----------------------|--------------------|-----------------|--|

| モデル           | SZ010                         | SZ030      | SZ130                | SZ310              | SZ410           |  |

| FPGA デバイス     | Xilinx                        | Xilinx     | Xilinx               | Xilinx             | Xilinx          |  |

| FIGA / / VI/  | Spartan-3                     | Spartan-3  | Spartan-3E           | Virtex-II Pro      | Virtex-4 FX     |  |

|               | (XC3S400)                     | (XC3S1000) | (XC3S1200E)          | (XC2VP4)           | (XC4VFX12)      |  |

| CPUコア         | MicroBlaze                    |            |                      | PowerPC405         |                 |  |

| CPU クロック      | 51.6096MHz                    |            | 265.4208MHz          | $350 \mathrm{MHz}$ |                 |  |

| 水晶発振器周波数      | 3.6864MHz                     |            |                      |                    | 100MHz          |  |

| DRAM          | 16MB                          |            | $16\text{MB}\times2$ | 32MB               | $32MB\times2$   |  |

| フラッシュメモリ      | 4MB                           | 8MB        | 8MB (SPI)            | 8MB                | 8MB (SPI)       |  |

| Ethernet      | 10BASE-T/100BASE-TX           |            |                      |                    |                 |  |

| 拡張 I/O ピン     | 86                            |            |                      | 70                 | 86              |  |

| シリアル          | 1ch(UART : 115.2kbps)         |            |                      |                    |                 |  |

| タイマ           | 2ch(OPB Timer : 1ch は OS で使用) |            |                      | PowerPC 内蔵タイマ      |                 |  |

| コンフィギュレーション   | TE7720                        |            | SPI<br>フラッシュメモリ      | TE7720             | SPI<br>フラッシュメモリ |  |

| 基板サイズ 72×47mm |                               |            |                      |                    |                 |  |

| 電源            | 電圧:+3.3V±3%                   |            |                      |                    |                 |  |

| リセット機能        | ソフトウェアリセット                    |            |                      |                    |                 |  |

| 標準 OS         | $\mu$ Clinux                  |            |                      | Linux              |                 |  |

## 1.3. 全体ブロック図

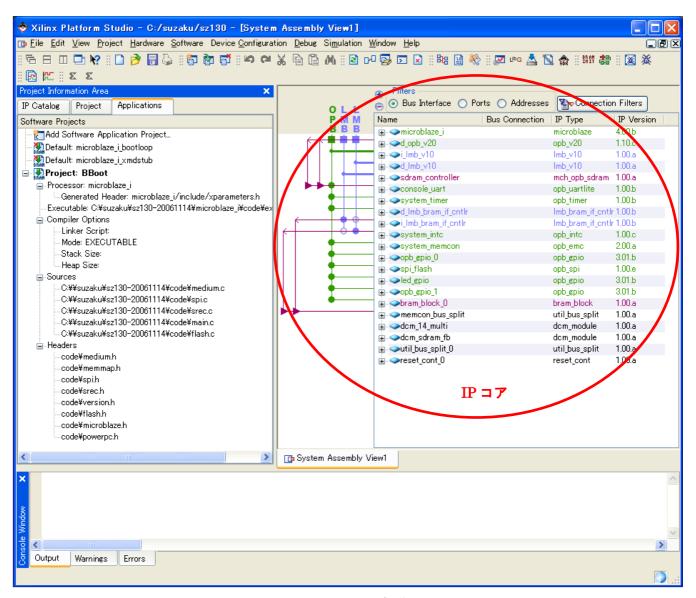

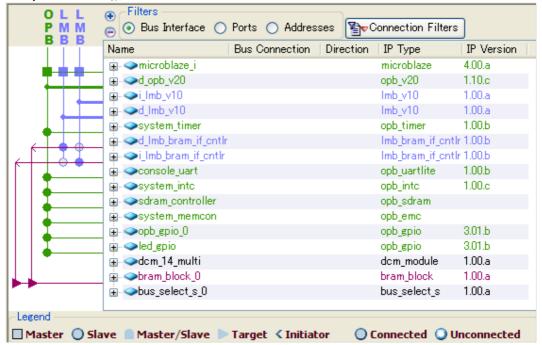

SUZAKU の全体ブロック図について説明をします。IP コアについてはここでは説明しません。"10.2.5 IP コア"をご参照ください。

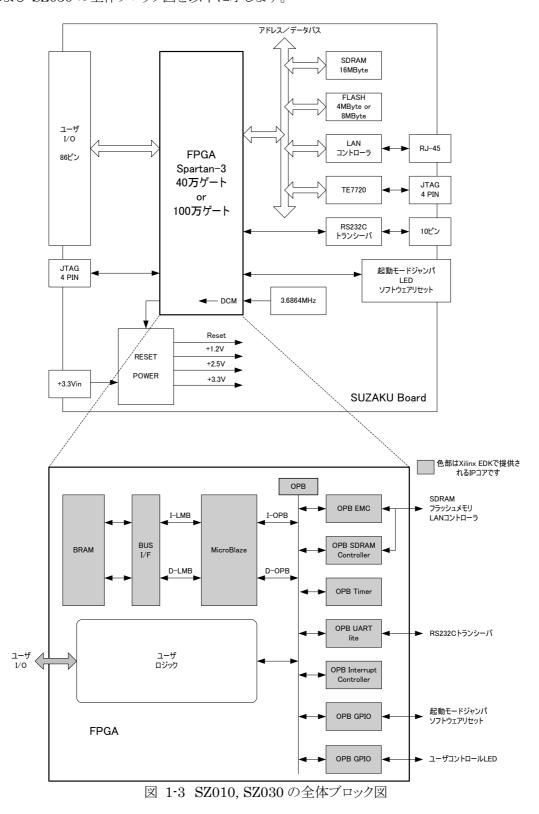

### 1.3.1. SZ010、SZ030

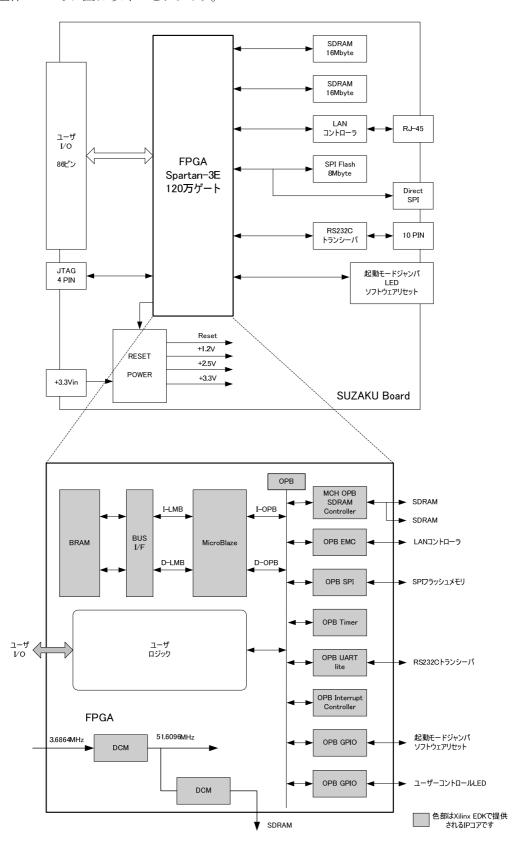

SZ010 および SZ030 の全体ブロック図を以下に示します。

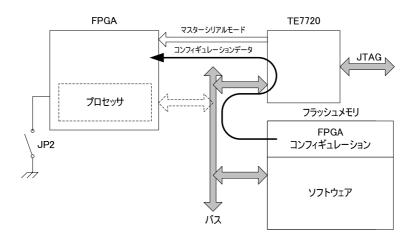

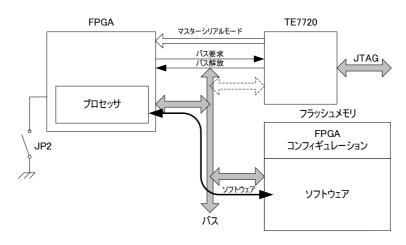

### 1.3.1.1. プロセッサ

FPGA 内部で MicroBlaze を使用しています。

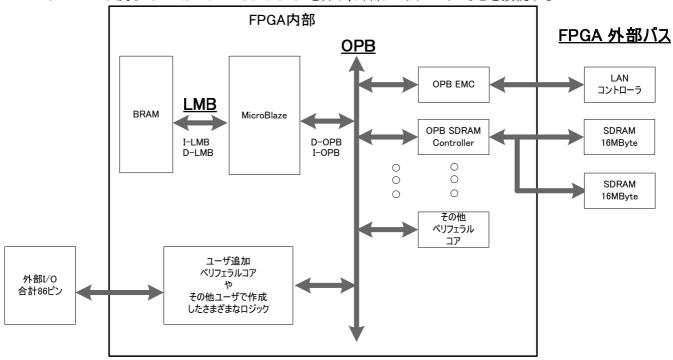

### 1.3.1.2. バス

- 3種類のバスで構成しています。

- ·FPGA 内部 LMB(Local Memory Bus)

MicroBlaze と BRAM(FPGA 内部メモリ)を接続する専用バス

·FPGA 内部 OPB(On-Chip Peripheral Bus)

複数のペリフェラル IP コアを接続するバス

**・FPGA** 外部バス

OPB EMC 及び OPB SDRAM Controller を介し、外部メモリデバイスなどを接続するバス

図 1-4 SZ010, SZ030 のバス

#### 1.3.1.3. メモリ

- 3種類のメモリで構成しています。

- ・FPGA 内部 BRAM (デフォルト 8kByte)

ブートプログラム用として使用しています。

起動完了後は、先頭の 32Byte(割り込みベクタ領域)以外であれば、ユーザプログラムで使用することもできます。

・FPGA 外部フラッシュメモリ

SZ010 は 4MByte、SZ030 は 8MByte を実装しています。

ブートローダ Hermit や Linux、FPGA コンフィギュレーションデータなどの保存に使用しています。 OPB-EMC を使用し、OPB と接続しています。

·FPGA 外部 SDRAM 16MByte

Linux のメインメモリとして使用しています。

OPB SDRAMController を使用し、OPB と接続しています。

### 1.3.1.4. シリアルコンソール

OS 用シリアルコンソールに OPB UART lite を使用しています。 OPB UART lite は RS-232Cトランシーバを 介し SUZAKU CON1 に接続しています。 RS-232Cトランシーバは、4 チャンネルタイプのものを実装しています。

### 1.3.1.5. LAN

LAN コントローラに、LAN91C111(メーカ: SMSC)を実装しています。LAN91C111 は OPB EMC を使用し OPBと接続しています。

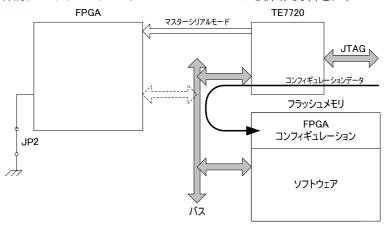

### 1.3.1.6. FPGA コンフィギュレーション

FPGA コンフィギュレーション IC に TE7720(メーカ:東京エレクトロンデバイス)を実装しています。TE7720 の詳細については"6.2.2 LBPlayer2で書き換える"をご参照ください。

図 1-5 SZ010, SZ030の主要部品配置図

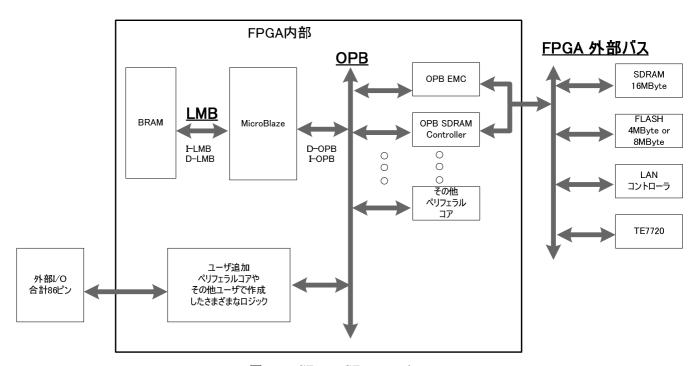

### 1.3.2. SZ130

SZ130 の全体のブロック図は以下のとおりです。

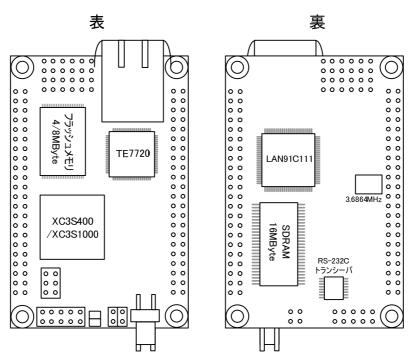

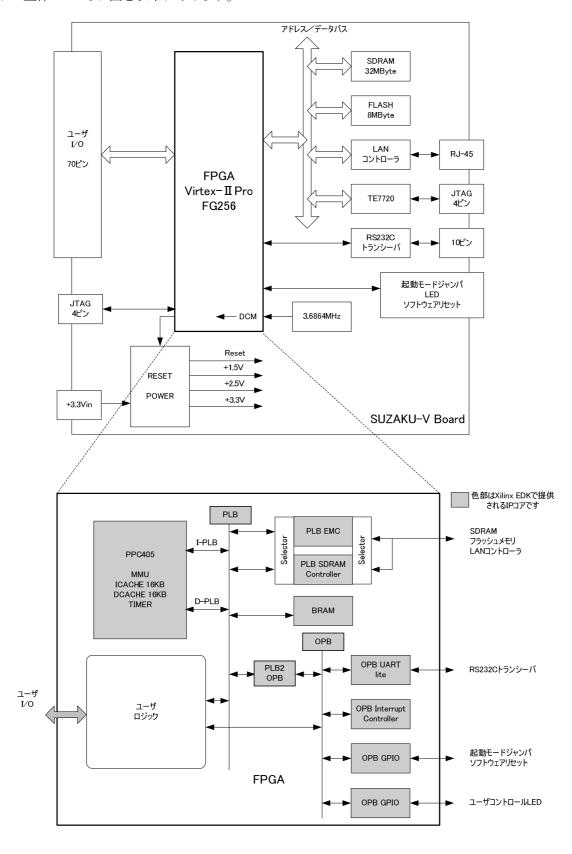

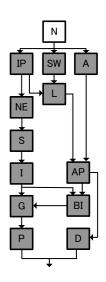

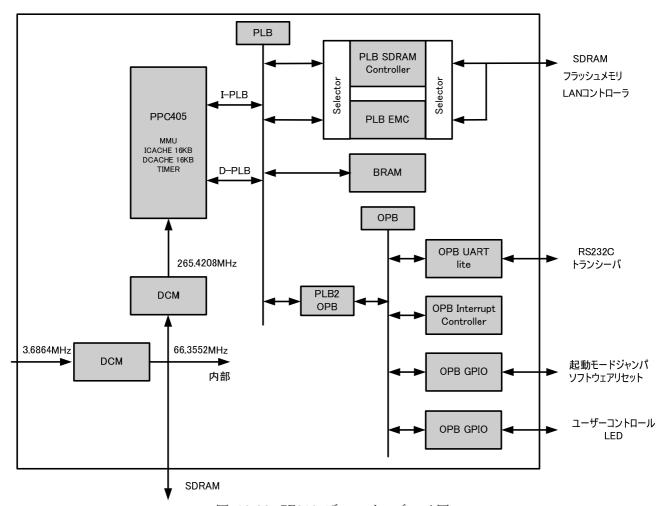

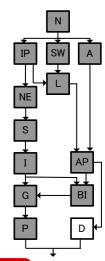

図 1-6 SZ130 の全体ブロック図

### 1.3.2.1. バス

- 3種類のバスで構成しています。

- ·FPGA 内部 LMB(Local Memory Bus)

MicroBlaze と BRAM(FPGA 内部メモリ)を接続する専用バス

·FPGA 内部 OPB(On-Chip Peripheral Bus)

複数のペリフェラル IP コアを接続するバス

•FPGA 外部バス

OPB EMC 及び OPB SDRAM Controller を介し、外部メモリデバイスなどを接続するバス

図 1-7 SZ130 のバス

### 1.3.2.2. プロセッサ

FPGA 内部で MicroBlaze を使用しています。

### 1.3.2.3. メモリ

- 3種類のメモリで構成しています。

- ・FPGA 内部 BRAM (デフォルト 8kByte)

ブートプログラム用として使用しています。

起動完了後は、先頭の 32Byte(割り込みベクタ領域)以外であれば、ユーザプログラムで使用することもできます。

・FPGA 外部 SPI フラッシュメモリ

8MByte を実装しています。

ブートローダ Hermit や Linux、FPGA コンフィグデータなどの保存に使用しています。

OPB SPI を使用し、OPB と接続しています。

·FPGA 外部 SDRAM 16MByte×2

Linux のメインメモリとして使用しています。

OPB SDRAM Controller を使用し、OPB と接続しています。

2枚のSDRAMの信号線は、完全に2つに分離して、FPGAと接続されています。

### 1.3.2.4. シリアルコンソール

OS 用シリアルコンソールに OPB UART lite を使用しています。 OPB UART lite は RS-232C トランシーバを 介し、SUZAKU CON1 に接続しています。 RS-232C トランシーバは、4 チャンネルタイプのものを実装しています。

### 1.3.2.5. LAN

LAN コントローラは LAN9115(メーカ:SMSC)を実装しています。 LAN9115 は OPB EMC を使用し OPB と接続しています。

### 1.3.2.6. FPGA コンフィギュレーション

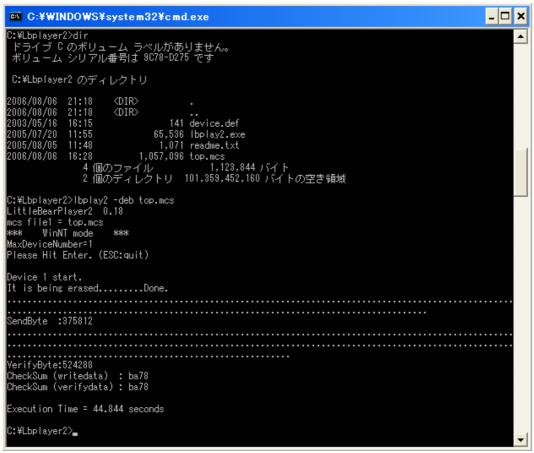

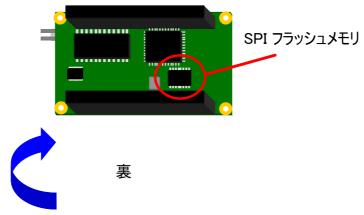

SPI コンフィギュレーションを採用しています。SPI フラッシュメモリは M25P64(メーカ:ST マイクロエレクトロニクス)を実装しています。SPI フラッシュメモリの詳細については"6.2.3 SPI Writer で書き換える"をご参照ください。

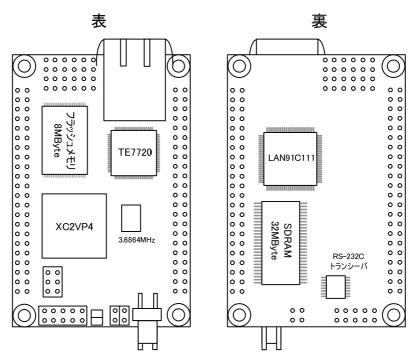

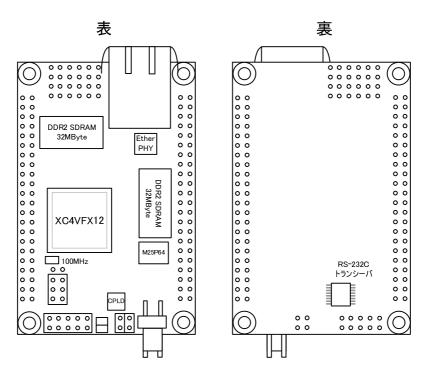

図 1-8 SZ130の主要部品配置図

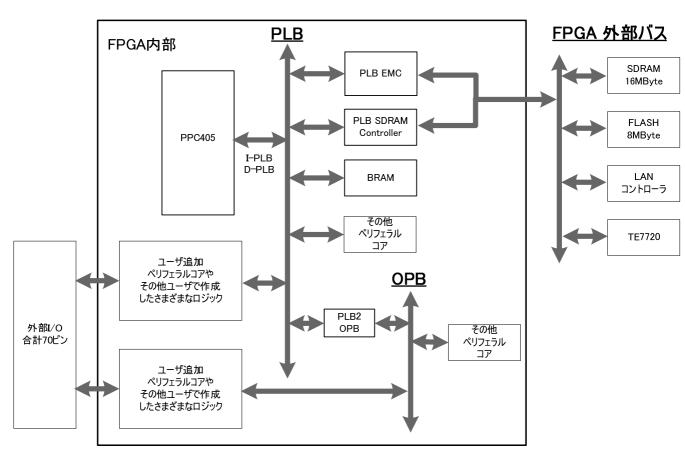

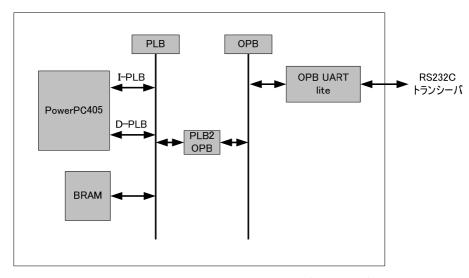

### 1.3.3. SZ310

SZ310 の全体のブロック図を以下に示します。

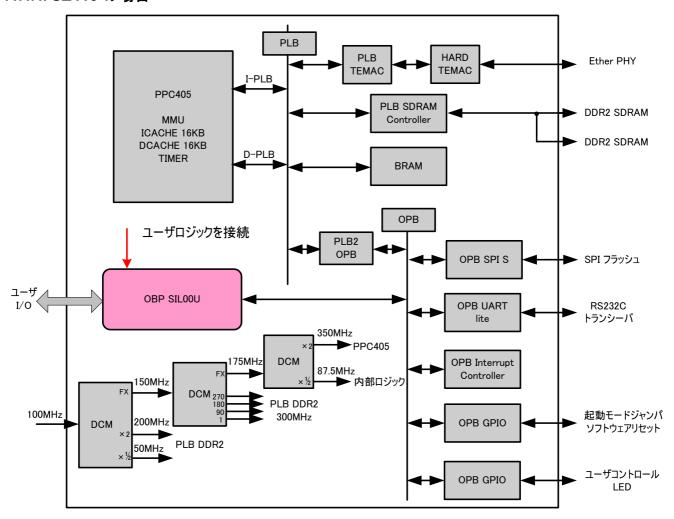

図 1-9 SZ310 の全体ブロック図

### 1.3.3.1. プロセッサ

FPGA 内部で PowerPC405 を使用しています。

### 1.3.3.2. バス

- 3種類のバスで構成しています。

- ·FPGA 内部 PLB(Processor Local Bus)

PowerPC405 と BRAM、PLB SDRAM Controller などのペリフェラル IP コアを接続するバス

- ·FPGA 内部 OPB(On-Chip Peripheral Bus)

- OPB UART lite、OPB INTC などのペリフェラル IP コアを接続するバス

- •FPGA 外部バス

PLB EMC 及び、PLB SDRAM Controller を介し、外部メモリデバイスなどを接続するバス

図 1-10 SZ310のバス

### 1.3.3.3. メモリ

- 3種類のメモリで構成しています。

- ・FPGA 内部 BRAM (デフォルト 16kByte)

ブートプログラム用として使用しています。

ブート完了後は、ユーザプログラムで使用することもできます。

・FPGA 外部フラッシュメモリ

8MByte を実装しています。

ブートローダ Hermit や Linux システム、FPGA コンフィグデータなどの保存に使用しています。 PLB EMC と接続しています。

·FPGA 外部 SDRAM 32MByte

Linux のメインメモリとして使用しています。

PLB SDRAM を使用し、PLB と接続しています。

### 1.3.3.4. シリアルコンソール

OS 用シリアルコンソールに OPB UART lite を使用しています。 OPB UART lite は RS-232C トランシーバを 介し、SUZAKU CON1 に接続しています。 RS-232C トランシーバは、4 チャンネルタイプのものを使用しています。

### 1.3.3.5. LAN

LAN コントローラに、FPGA 外部に LAN91C111(メーカ:SMSC)を実装しています。 LAN91C111 は、PLB EMC を使用し、PLB と接続しています。

### 1.3.3.6. FPGA コンフィギュレーション

FPGA コンフィギュレーション IC に TE7720(メーカ:東京エレクトロンデバイス)を実装しています。TE7720 の詳細については"6.2.2 LBPlayer2で書き換える"をご参照ください。

図 1-11 SZ310の主要部品配置図

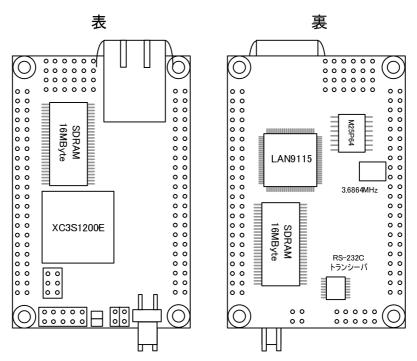

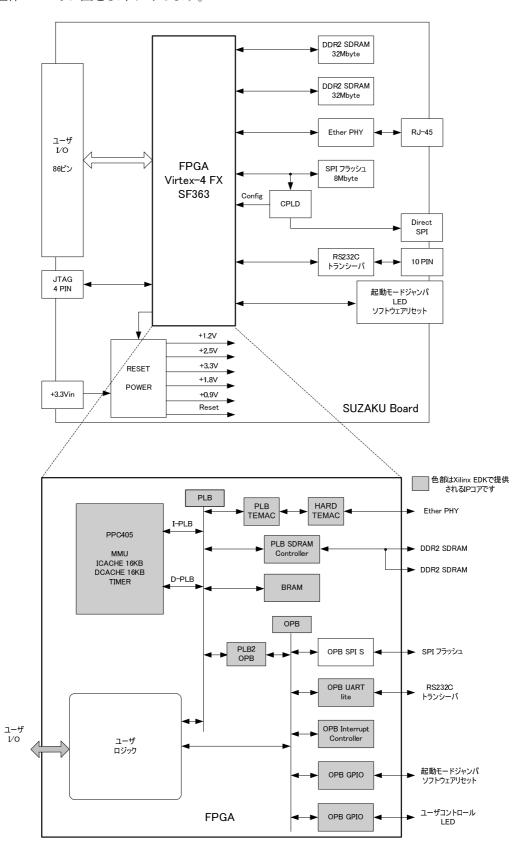

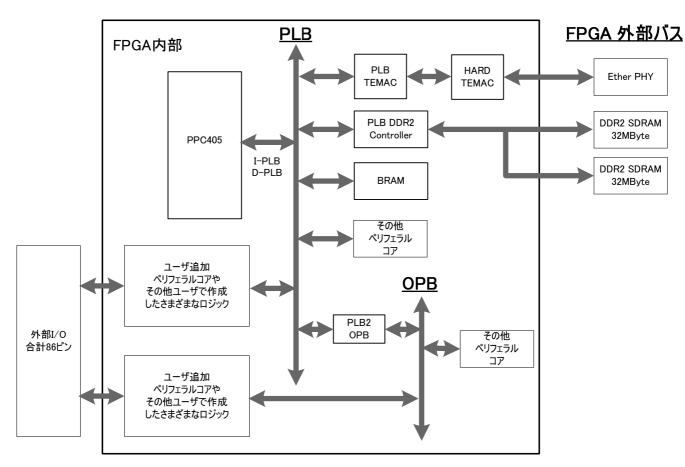

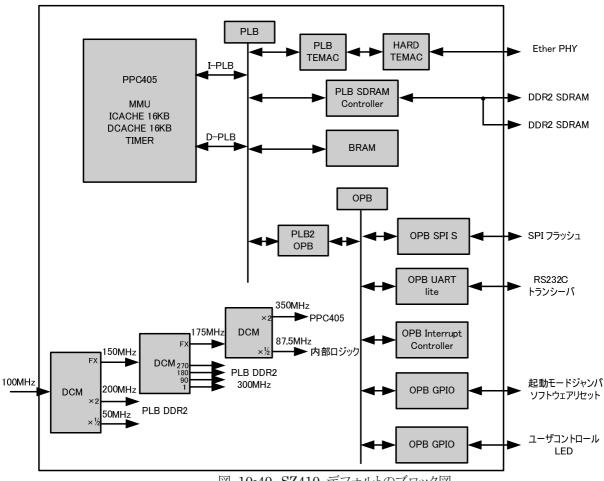

### 1.3.4. SZ410

SZ410 の全体のブロック図を以下に示します。

図 1-12 SZ410 の全体ブロック図

### 1.3.4.1. プロセッサ

FPGA 内部で PowerPC405 を使用しています。

### 1.3.4.2. バス

- 3種類のバスで構成しています。

- ·FPGA 内部 PLB(Processor Local Bus)

PowerPC405 と BRAM、PLB DDR2 Controller などのペリフェラル IP コアを接続するバス

- ·FPGA 內部 OPB(On-Chip Peripheral Bus)

- OPB UART lite、OPB INTC などのペリフェラル IP コアを接続するバス

- **・FPGA** 外部バス

PLB DDR2 Controller 等を介し、外部メモリデバイスなどを接続するバス

図 1-13 SZ410のバス

### 1.3.4.3. メモリ

- 3種類のメモリで構成しています。

- ・FPGA 内部 BRAM (デフォルト 16kByte)

ブートプログラム用として使用しています。

ブート完了後は、ユーザプログラムで使用することもできます。

・FPGA 外部 SPI フラッシュメモリ

8MByte を実装しています。

ブートローダ Hermit や Linux システム、FPGA コンフィグデータなどの保存に使用しています。 OPB SPI S を使用し、OPB と接続しています。

·FPGA 外部 DDR2 SDRAM 32MByte×2

Linux のメインメモリとして使用しています。

PLB DDR2 Controller と接続しています。

2 枚の DDR2 SDRAM の信号線は完全に 2 つに分離して、FPGA と接続されています。

### 1.3.4.4. シリアルコンソール

OS 用シリアルコンソールに OPB UART lite を使用しています。 OPB UART lite は RS-232C トランシーバを 介し、SUZAKU CON1 に接続しています。 RS-232C トランシーバは、4 チャンネルタイプのものを使用しています。

### 1.3.4.5. LAN

Virtex-4 FX 内蔵の TEMAC (Tri-Mode Ether MAC)と 10BASE-T/100BASE-TX の Ethrer PHY (メーカ: SMSC)を使用しています

### 1.3.4.6. FPGA コンフィギュレーション

CPLD を使用した SPI コンフィギュレーションを採用しています。 SPI フラッシュメモリは M25P64(メーカ:ST マイクロエレクトロニクス)を実装しています。 SPI フラッシュメモリの詳細については"6.2.3 SPI Writer で書き換える"をご参照ください。

図 1-14 SZ410の主要部品配置図

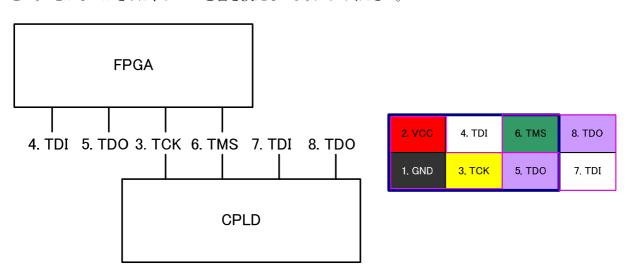

# **X**TIPS SZ410 の JTAG(CON7) コネクタの横のスルーホールは?

SZ410 の JTAG(CON7)コネクタの横のスルーホールは CPLD 書き込み用のスルーホールです。FPGA と CPLD の JTAG ピンは以下の図のように TCK、TMS を共用する形で配線されています。 CPLD を書き換えること はもちろん出来ますが、書き換えに失敗してしまうと SUZAKU が動くようになるまでの復旧が大変なので、どうしても ということがないかぎりは、CPLDを書き換えないようにしてください。

# TIPS SZ410 CPLD と SPI フラッシュの採用理由

CPLD と SPI フラッシュメモリを採用したのは、シリアルビットストリームである SPI はそのままマスターシリアルに 置き換えることが容易であり、また 8mm×6mmの SPI フラッシュメモリと 5mm×5mm の CPLD(XC2C32QFP32 ピン)を使用すると、基板上の設置面積が小さくてすむからです。

## 1.4. メモリマップ

## 1.4.1. SZ010、SZ030

SZ010 および SZ030 のメモリマップは以下のとおりです。

表 1-2 SZ010、SZ030 のメモリマップ

| Start Address | End Address | ペリフェラル                   | デバイス                   |

|---------------|-------------|--------------------------|------------------------|

| 0x0000 0000   | 0x0000 1FFF | BRAM                     |                        |

| 0x0000 2000   | 0x7FFF FFFF | Reserved                 |                        |

| 0x8000 0000   | 0x80FF FFFF | OPB-SDRAM Controller     | SDRAM 16MByte          |

| 0x8100 0000   | 0xFEFF FFFF | Free                     |                        |

| 0xFF00 0000   | 0xFF7F FFFF | OPB-EMC                  | Flash 4MByte or 8MByte |

| 0xFF80 0000   | 0xFFDF FFFF | Free                     |                        |

| 0xFFE0 0000   | 0xFFEF FFFF | OPB-EMC                  | LAN コントローラ             |

| 0xFFF0 0000   | 0xFFFF 0FFF | Free                     |                        |

| 0xFFFF 1000   | 0xFFFF 10FF | OPB-Timer                |                        |

| 0xFFFF 1100   | 0xFFFF 1FFF | Free                     |                        |

| 0xFFFF 2000   | 0xFFFF 20FF | OPB-UART lite            | RS-232C                |

| 0xFFFF 2100   | 0xFFFF 2FFF | Free                     |                        |

| 0xFFFF 3000   | 0xFFFF 30FF | OPB-Interrupt Controller |                        |

| 0xFFFF 3100   | 0xFFFF 9FFF | Free                     |                        |

| 0xFFFF A000   | 0xFFFF A1FF | OPB-GPIO                 | ブートモードジャンパ             |

|               |             |                          | ソフトウェアリセット             |

| 0xFFFF A200   | 0xFFFF A3FF | OPB-LED                  | LED                    |

| 0xFFFF A400   | 0xFFFF FFFF | Free                     |                        |

## 1.4.2. SZ130

SZ130 のメモリマップは以下のとおりです。

表 1-3 SZ130 のメモリマップ

| Start Address | End Address | ペリフェラル                   | デバイス             |

|---------------|-------------|--------------------------|------------------|

| 0x0000 0000   | 0x0000 1FFF | BRAM                     |                  |

| 0x0000 2000   | 0x7FFF FFFF | Reserved                 |                  |

| 0x8000 0000   | 0x81FF FFFF | OPB-SDRAM Controller     | SDRAM 32MByte    |

| 0x8200 0000   | 0xFEFF FFFF | Free                     |                  |

| 0xFF00 0000   | 0xFF00 01FF | OPB-SPI                  | SPI Flash 8MByte |

| 0xFF00 0200   | 0xFFDF FFFF | Free                     |                  |

| 0xFFE0 0000   | 0xFFE0 FFFF | OPB-EMC                  | LAN コントローラ       |

| 0xFFE1 0000   | 0xFFFF 0FFF | Free                     |                  |

| 0xFFFF 1000   | 0xFFFF 10FF | OPB-Timer                |                  |

| 0xFFFF 1100   | 0xFFFF 1FFF | Free                     |                  |

| 0xFFFF 2000   | 0xFFFF 20FF | OPB-UART lite            | RS-232C          |

| 0xFFFF 2100   | 0xFFFF 2FFF | Free                     |                  |

| 0xFFFF 3000   | 0xFFFF 30FF | OPB-Interrupt Controller |                  |

| 0xFFFF 3100   | 0xFFFF 9FFF | Free                     |                  |

| 0xFFFF A000   | 0xFFFF A1FF | OPB-GPIO                 | ブートモードジャンパ       |

|               |             |                          | ソフトウェアリセット       |

| 0xFFFF A200   | 0xFFFF A3FF | OPB-LED                  | LED              |

| 0xFFFF A400   | 0xFFFF FFFF | Free                     |                  |

#### 1.4.3. SZ310

SZ310 のメモリマップは以下のとおりです。

表 1-4 SZ310 のメモリマップ

| Start Address | End Address | ペリフェラル                   | デバイス          |

|---------------|-------------|--------------------------|---------------|

| 0x0000 0000   | 0x01FF FFFF | PLB-SDRAM Controller     | SDRAM 32MByte |

| 0x0200 0000   | 0xEFFF FFFF | Free                     |               |

| 0xF000 0000   | 0xF07F FFFF | PLB-EMC                  | Flash 8MByte  |

| 0xF080 0000   | 0xF0DF FFFF | Free                     |               |

| 0xF0E0 0000   | 0xF0EF FFFF | PLB-EMC                  | LAN コントローラ    |

| 0xF0F0 0000   | 0xF0FF 1FFF | Free                     |               |

| 0xF0FF 2000   | 0xF0FF 20FF | OPB-UART lite            | RS-232C       |

| 0xF0FF 2100   | 0xF0FF 2FFF | Free                     |               |

| 0xF0FF 3000   | 0xF0FF 30FF | OPB-Interrupt Controller |               |

| 0xF0FF 3100   | 0xF0FF 9FFF | Free                     |               |

| 0xF0FF A000   | 0xF0FF A1FF | OPB-GPIO                 | ブートモードジャンパ    |

|               |             |                          | ソフトウェアリセット    |

| 0xF0FF A200   | 0xF0FF A3FF | OPB-LED                  | LED           |

| 0xF0FF A400   | 0xFFFF BFFF | Free                     |               |

| 0xFFFF C000   | 0xFFFF FFFF | BRAM                     |               |

#### 1.4.4. SZ410

SZ410 のメモリマップは以下のとおりです。

表 1-5 SZ410 のメモリマップ

| Start Address | End Address | ペリフェラル                   | デバイス               |

|---------------|-------------|--------------------------|--------------------|

| 0x0000 0000   | 0x03FF FFFF | PLB-DDR2 Controller      | DDR2 SDRAM 64MByte |

| 0x0400 0000   | 0xF0DF FFFF | Free                     |                    |

| 0xF0E0 0000   | 0xF0E0 FFFF | PLB-TEMAC                | Ether PHY          |

| 0xF0E1 0000   | 0xF0FE FFFF | Free                     |                    |

| 0xF0FF 0000   | 0xF0FF 01FF | OPB-SPI S                | SPI Flash 8MByte   |

| 0xF0FF 0200   | 0xF0FF 1FFF | Free                     |                    |

| 0xF0FF 2000   | 0xF0FF 20FF | OPB-UART lite            | RS-232C            |

| 0xF0FF 2100   | 0xF0FF 2FFF | Free                     |                    |

| 0xF0FF 3000   | 0xF0FF 30FF | OPB-Interrupt Controller |                    |

| 0xF0FF 3100   | 0xF0FF 9FFF | Free                     |                    |

| 0xF0FF A000   | 0xF0FF A1FF | OPB-GPIO                 | ブートモードジャンパ         |

|               |             |                          | ソフトウェアリセット         |

| 0xF0FF A200   | 0xF0FF A3FF | OPB-LED                  | LED                |

| 0xF0FF A400   | 0xFFFF BFFF | Free                     |                    |

| 0xFFFF C000   | 0xFFFF FFFF | BRAM                     |                    |

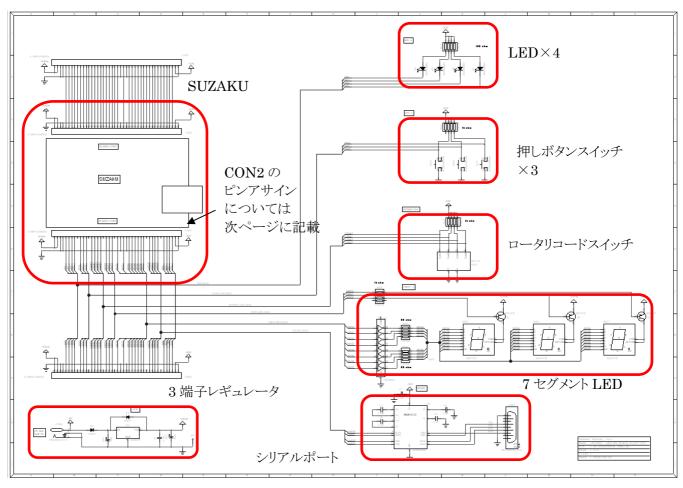

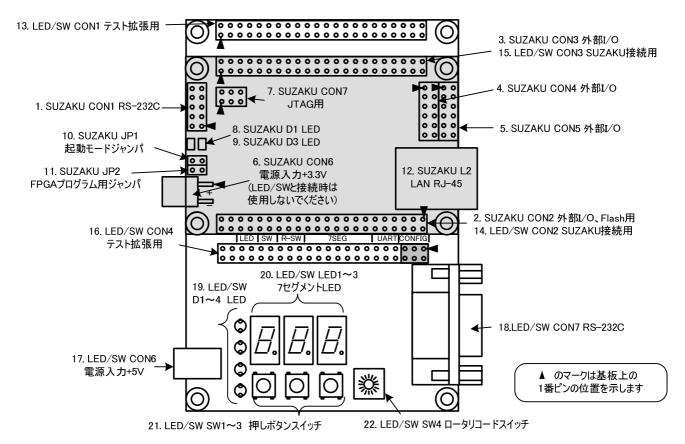

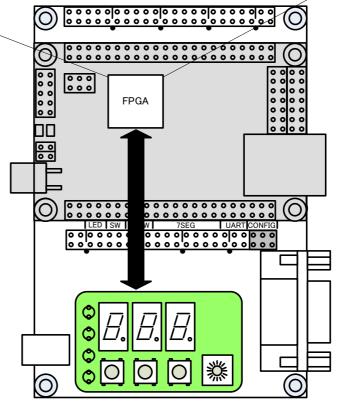

# 2.LED/SW ボードについて

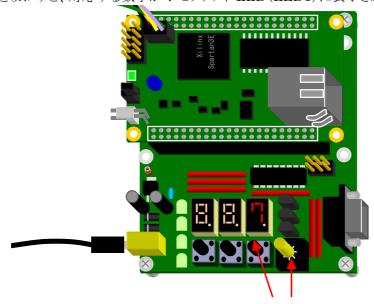

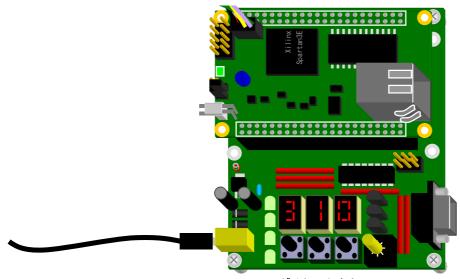

SUZAKU スターターキットは"SUZAKU+LED/SW ボード"で構成されます。LED/SW ボードは SUZAKU の学習用ボードとして生み出されました。LED/SW ボードについて回路図をみながら簡単に説明します。詳細については"7 ISE の使い方"で実際に LED/SW ボードに触りながら説明します。

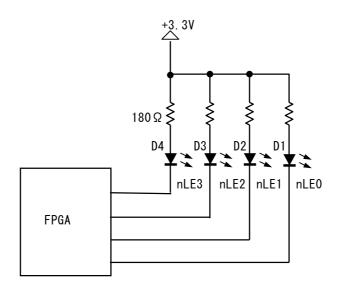

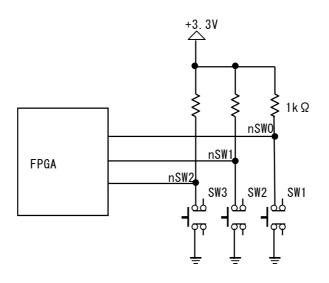

## 2.1. 回路説明

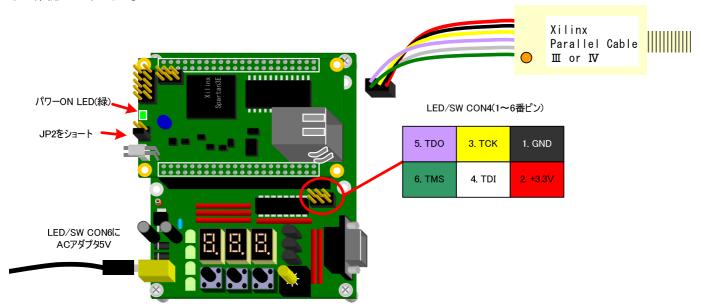

以下の回路図が LED/SW ボードの回路図です。回路図及び部品表は付属 CD-ROM の

"¥suzaku-starter-kit¥doc"に収録されているので詳細はそちらをご参照ください。

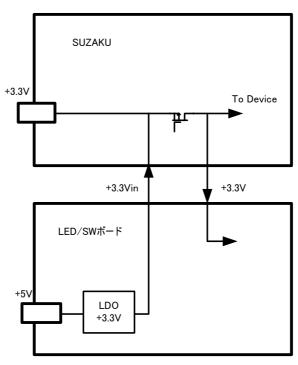

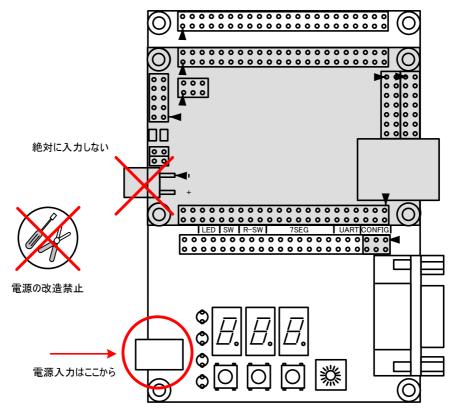

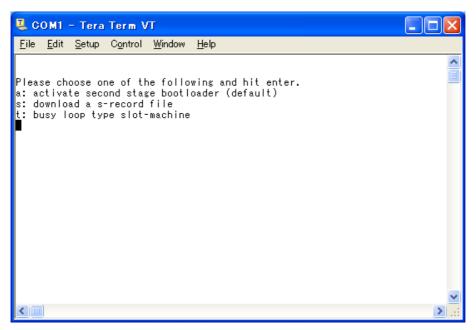

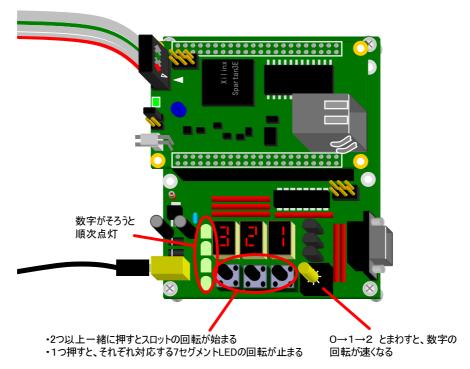

LED/SW ボードには単色 LED が 4 つ (D1、D2、D3、D4)、押しボタンスイッチが 3 つ (SW1、SW2、SW3)、ロータリコードスイッチが 1 つ (SW4)、7 セグメント LED が 3 つ (LED1、LED2、LED3)、シリアルポートが 1 つ実装されており、それぞれ CON2 から SUZAKU と接続するようになっています。安定した+3.3V を得るため AC アダプタ 5V から 3 端子レギュレータで+3.3V を作っています。この+3.3V は CON2、CON3から SUZAKU 側へ供給されます。

図 2-1 LED/SW 回路図(縮小版)

# 2.2. ピンアサイン

LED/SW ボードを使用する際に必要となるピンアサインを以下に示します。 その他の SUZAKU+LED/SW ボードのピンアサインについては"13 SUZAKU+LED/SW ボードのピンアサイン"をご参照ください。

表 2-1 クロック、リセット信号 ピンアサイン

|    |         |     |        | FPGA 接続先 |       |       |       |

|----|---------|-----|--------|----------|-------|-------|-------|

| 番号 | 信号名     | I/O | 機能     | SZ010    | SZ130 | SZ310 | SZ410 |

|    |         |     |        | SZ030    |       |       |       |

|    | SYS_CLK | I   | クロック信号 | Т9       | U10   | C8    | Y6    |

|    | SYS_RST | I   | リセット信号 | F5       | D3    | A8    | U3    |

表 2-2 機能用ピンアサイン(CON2)

|    |        |     | FPGA 接続先        |                |       |       |       |

|----|--------|-----|-----------------|----------------|-------|-------|-------|

| 番号 | 信号名    | I/O | 機能              | SZ010<br>SZ030 | SZ130 | SZ310 | SZ410 |

| 8  | UART3  | I   | RTS             | A7             | N4    | E14   | D15   |

| 9  | UART2  | 0   | TXD             | A3             | M6    | E13   | E15   |

| 10 | UART1  | 0   | CTS             | D5             | M5    | F12   | F15   |

| 11 | UART0  | I   | RXD             | B4             | M3    | F13   | P4    |

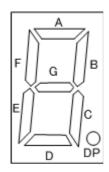

| 13 | SEG7   | 0   | セグメント DP        | C5             | L5    | F15   | P1    |

| 14 | SEG6   | 0   | セグメントG          | B5             | L6    | F16   | P2    |

| 15 | SEG5   | 0   | セグメント F         | E6             | L4    | G13   | L2    |

| 16 | SEG4   | 0   | セグメント E         | D6             | L3    | G14   | M2    |

| 17 | SEG3   | 0   | セグメント D         | C6             | L2    | G15   | N2    |

| 18 | SEG2   | 0   | セグメントC          | В6             | L1    | G16   | N3    |

| 20 | SEG1   | 0   | セグメント B         | A8             | С9    | N9    | Y7    |

| 22 | SEG0   | 0   | セグメントA          | В8             | D9    | P9    | W7    |

| 24 | nSEL2  | 0   | 7 セグメント LED3 選択 | D7             | K6    | H13   | N5    |

| 25 | nSEL1  | 0   | 7 セグメント LED2 選択 | C7             | K4    | H14   | M3    |

| 26 | nSEL0  | 0   | 7 セグメント LED1選択  | В7             | K3    | H15   | M4    |

| 28 | nCODE3 | I   | ロータリコードスイッチ 23  | C8             | J1    | J16   | H5    |

| 29 | nCODE2 | I   | ロータリコードスイッチ 22  | A9             | F9    | J15   | E2    |

| 30 | nCODE1 | I   | ロータリコードスイッチ 21  | A12            | E9    | J14   | D2    |

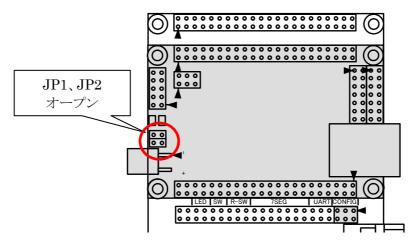

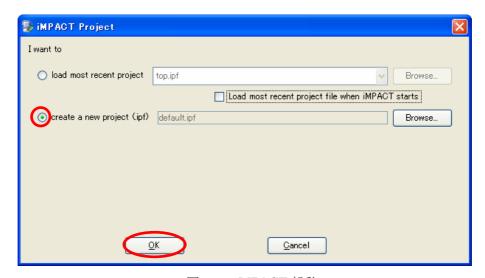

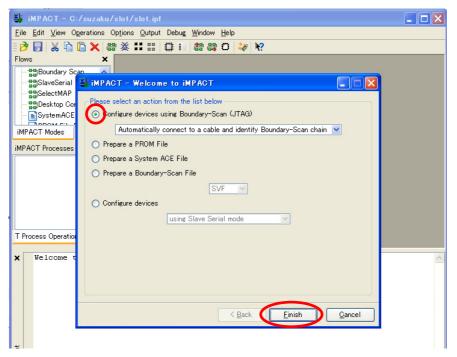

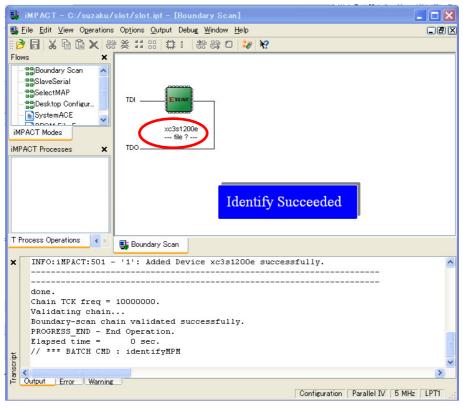

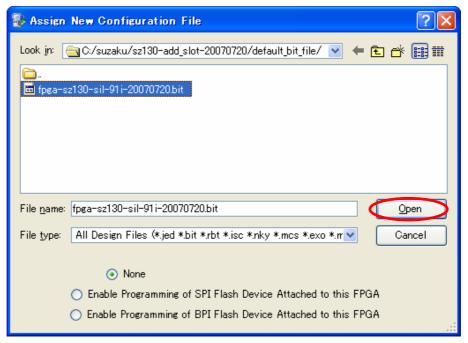

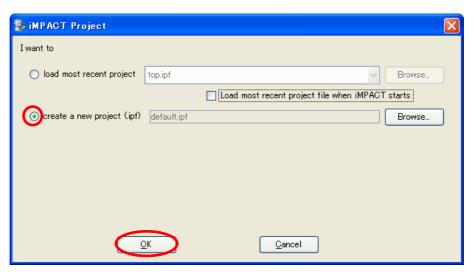

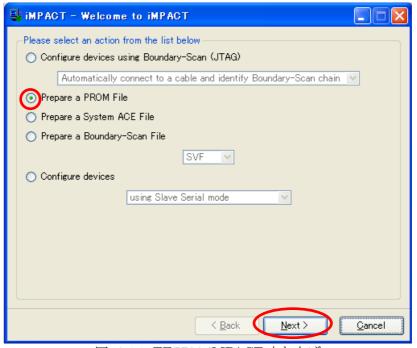

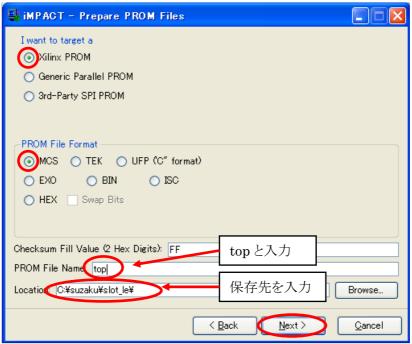

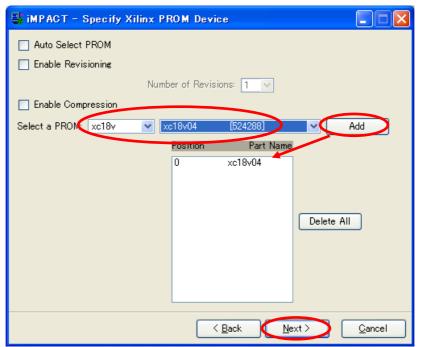

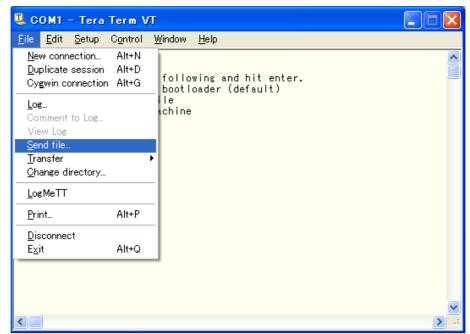

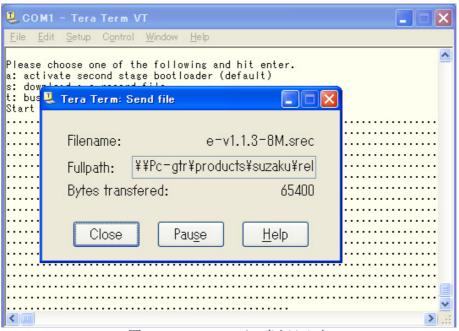

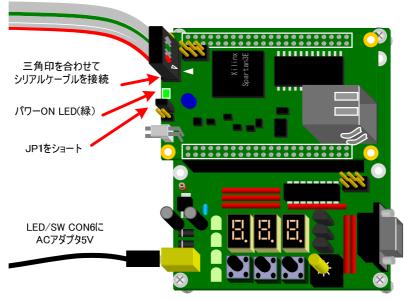

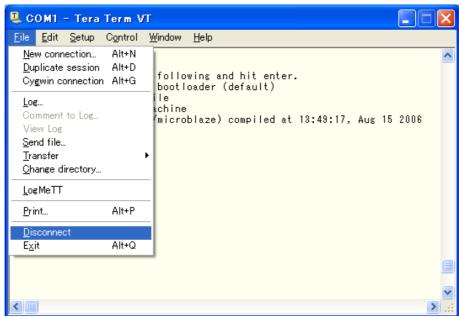

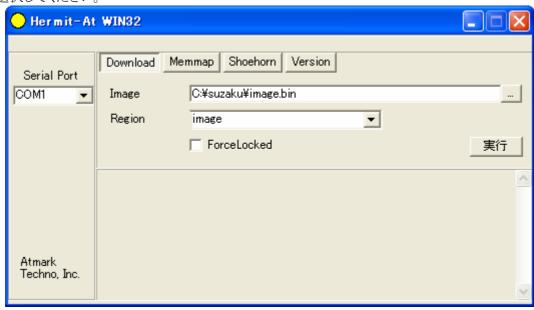

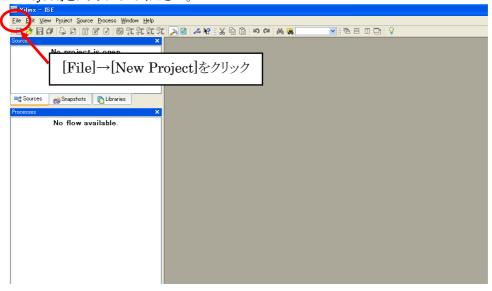

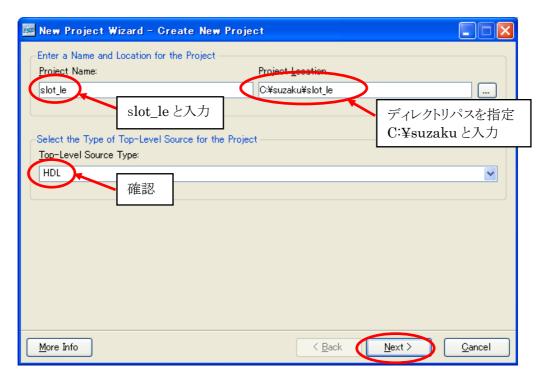

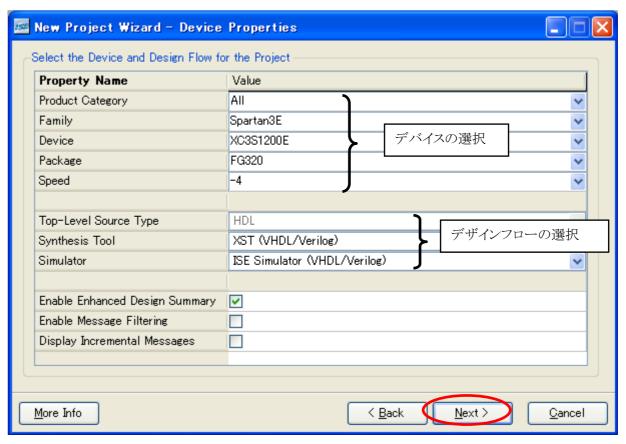

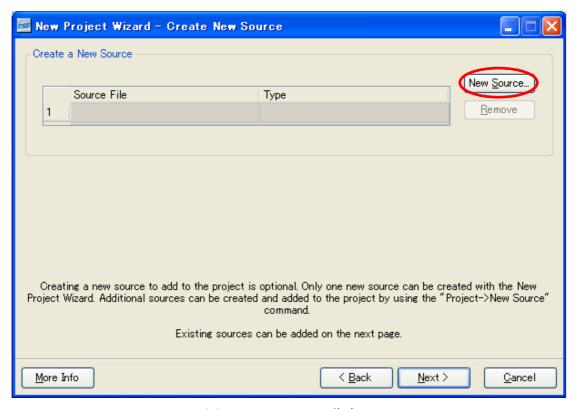

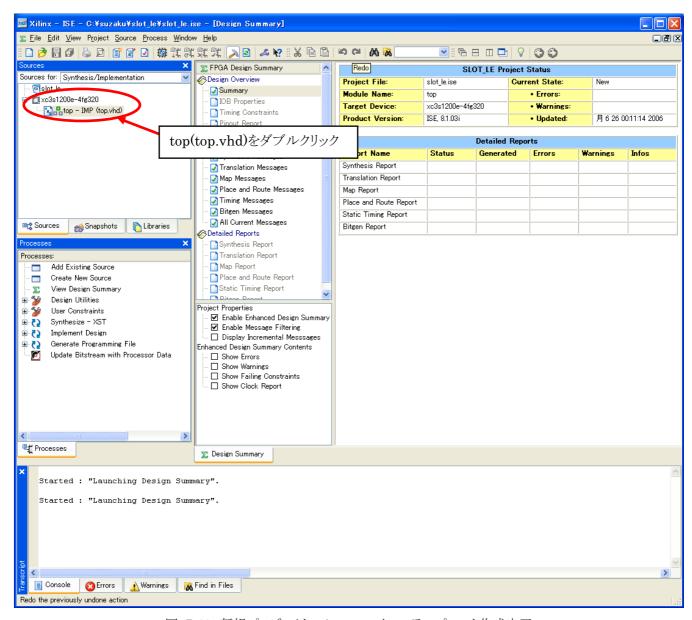

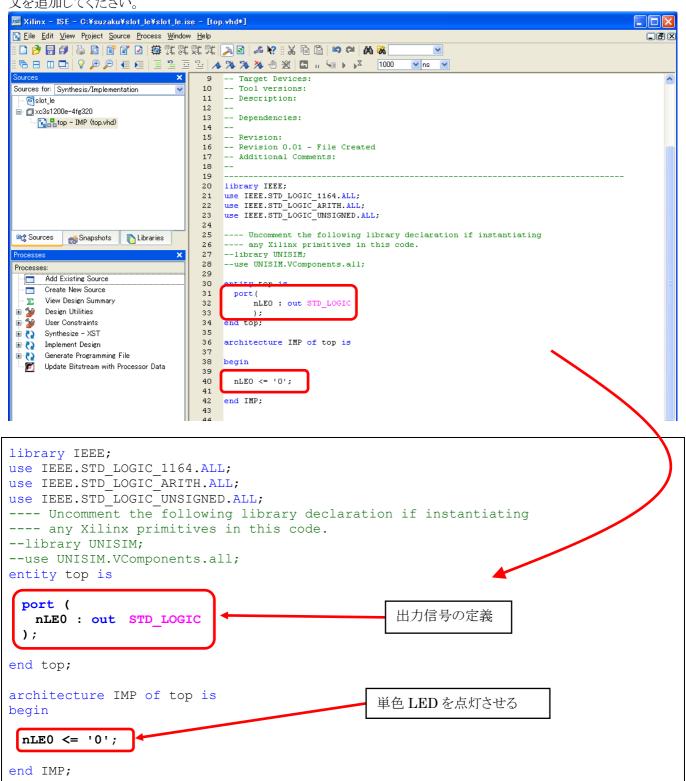

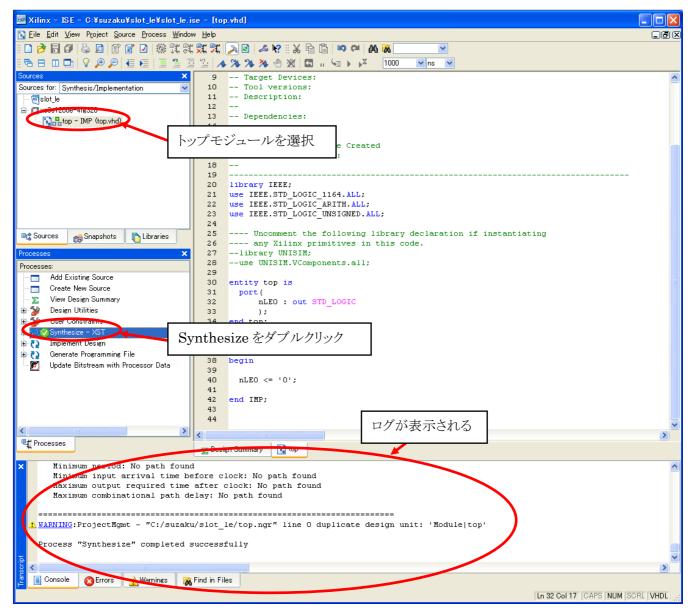

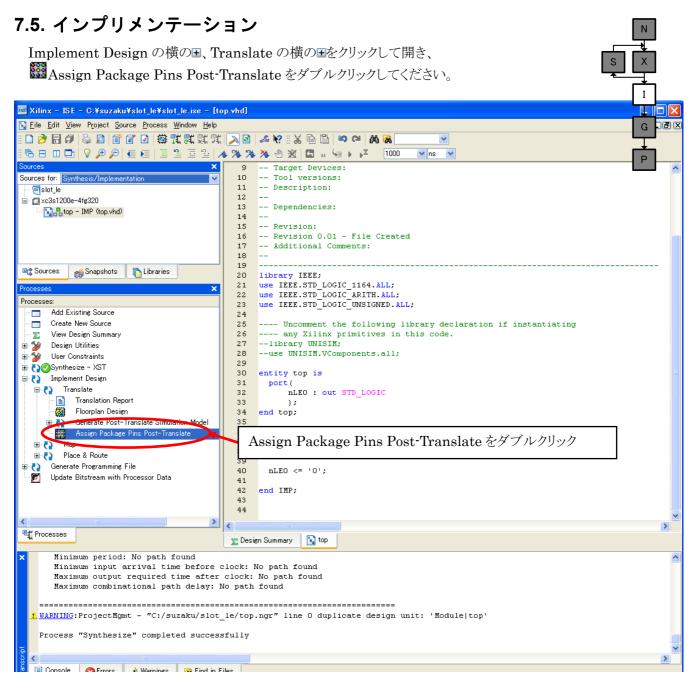

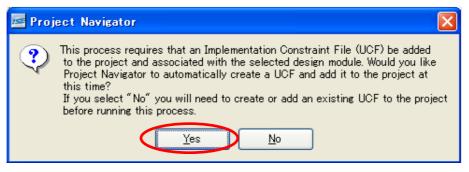

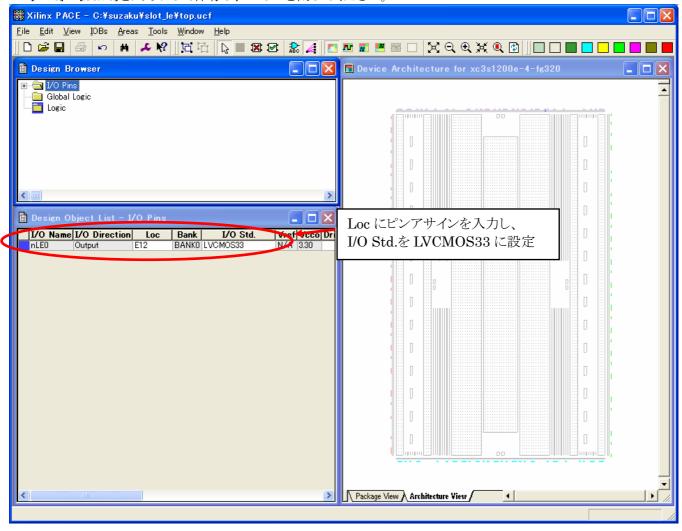

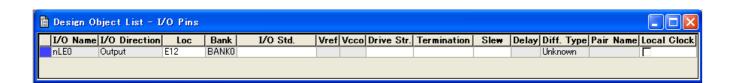

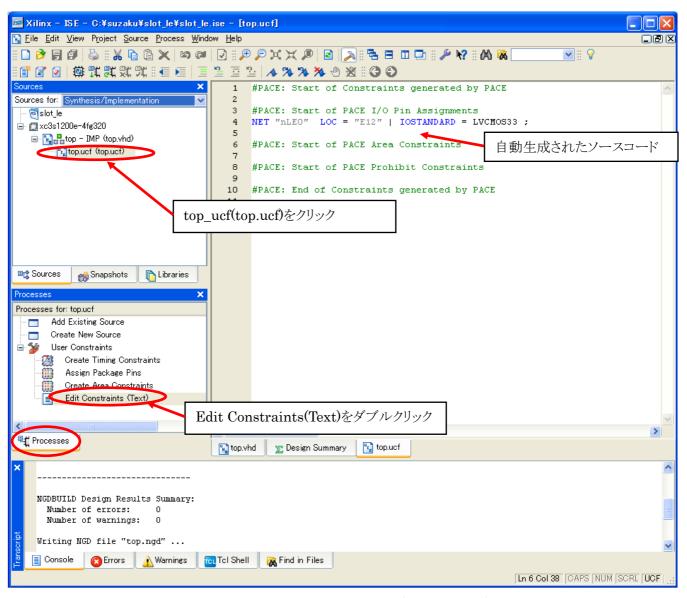

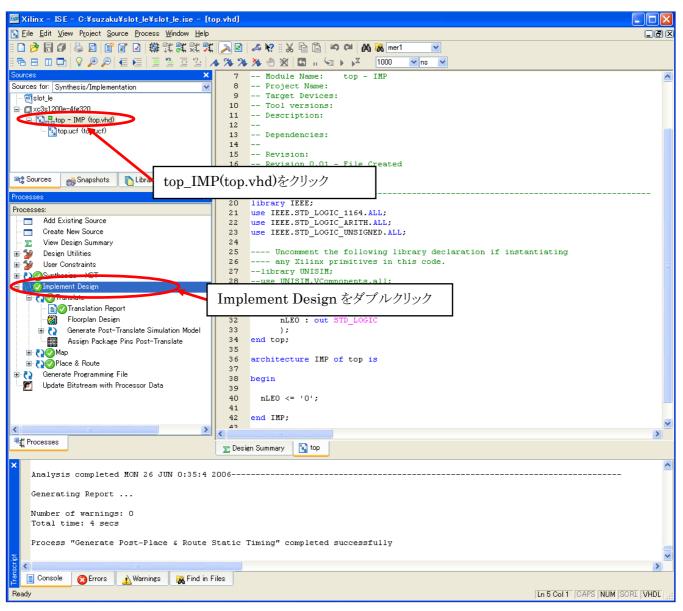

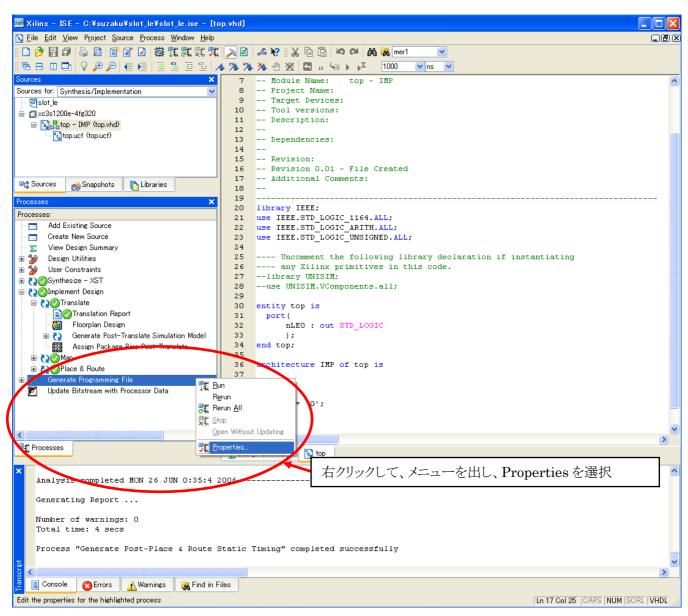

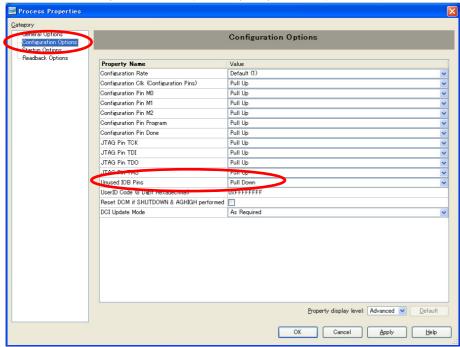

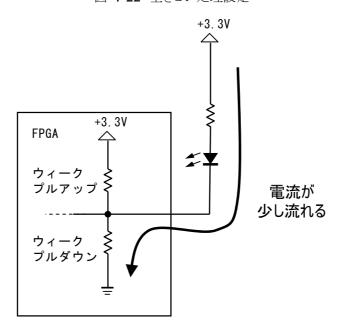

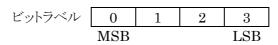

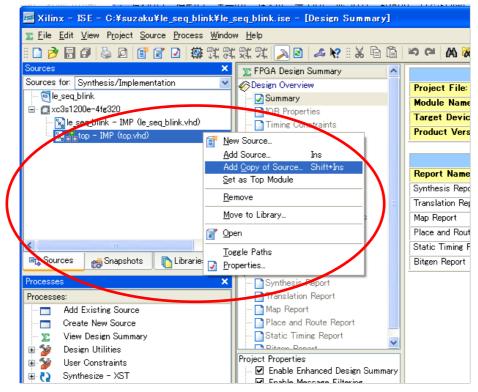

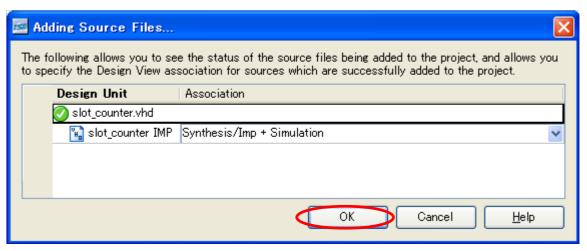

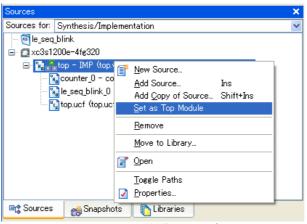

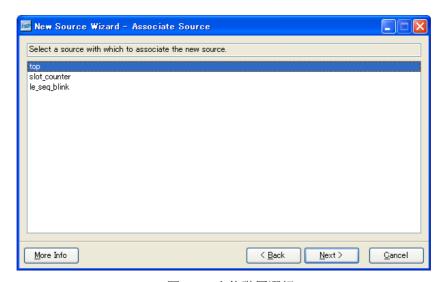

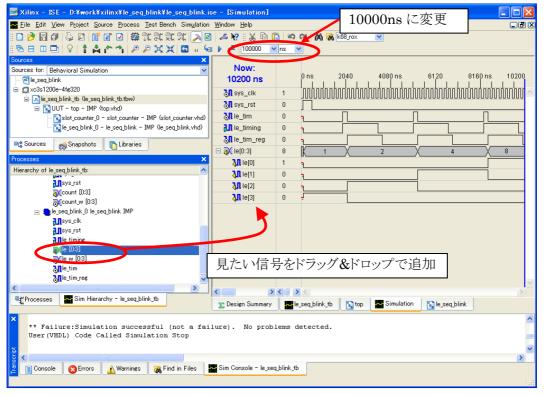

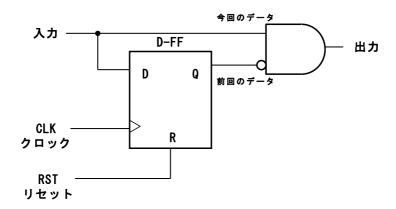

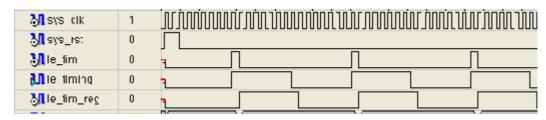

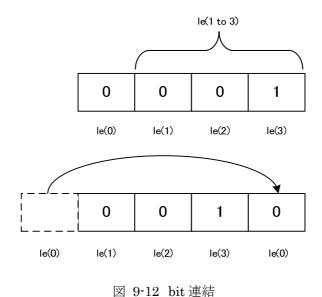

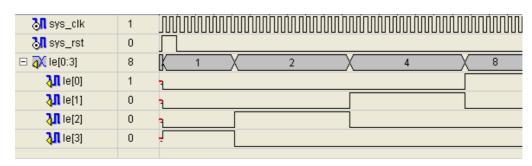

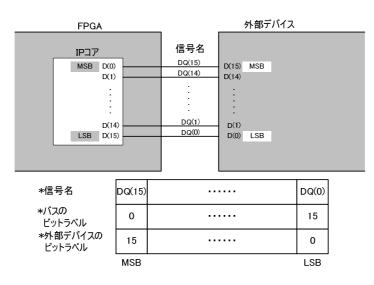

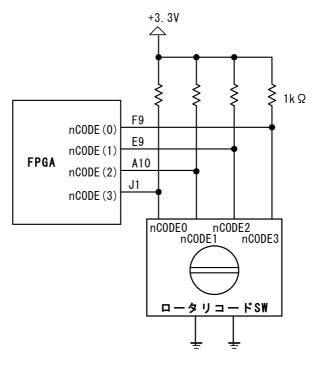

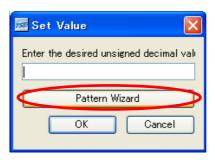

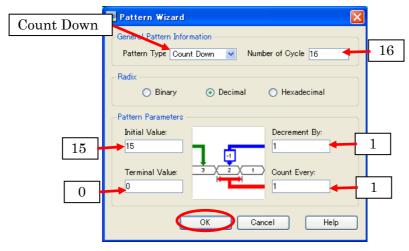

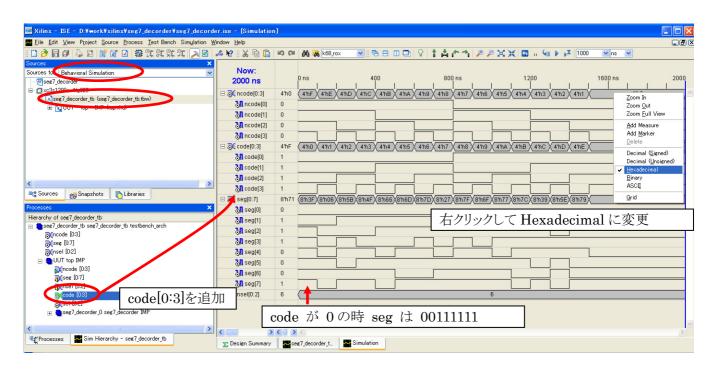

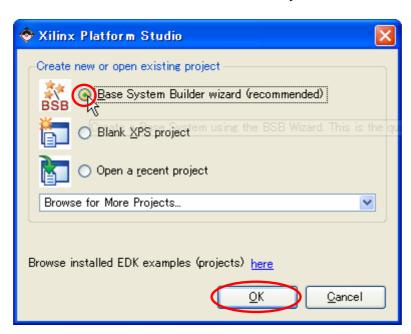

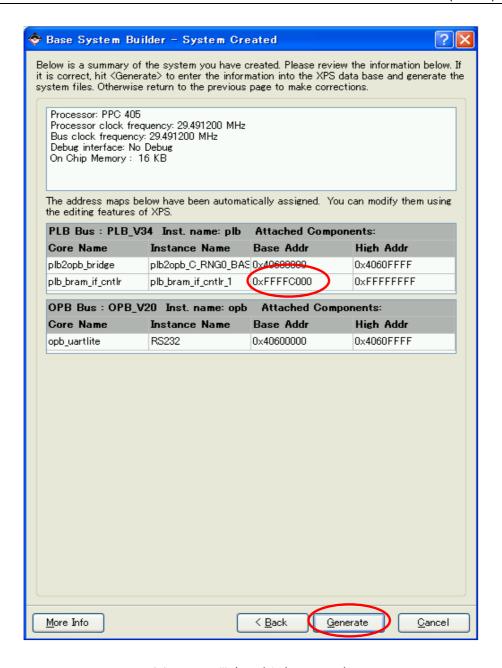

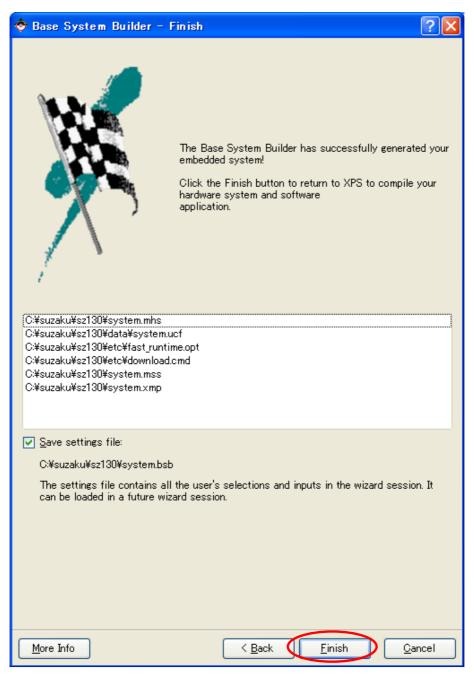

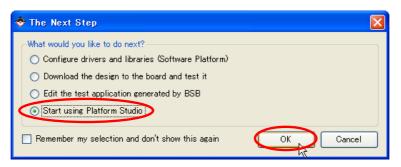

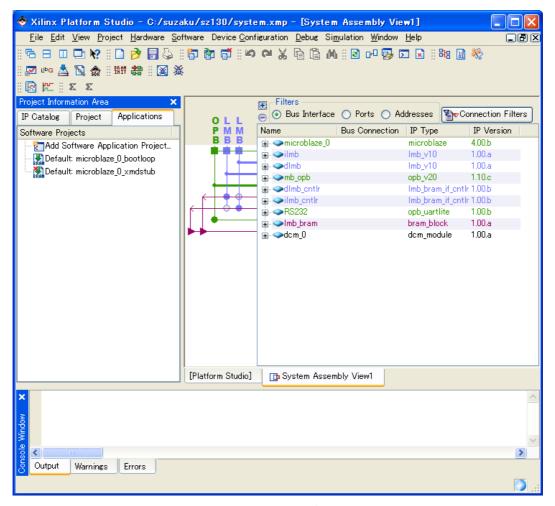

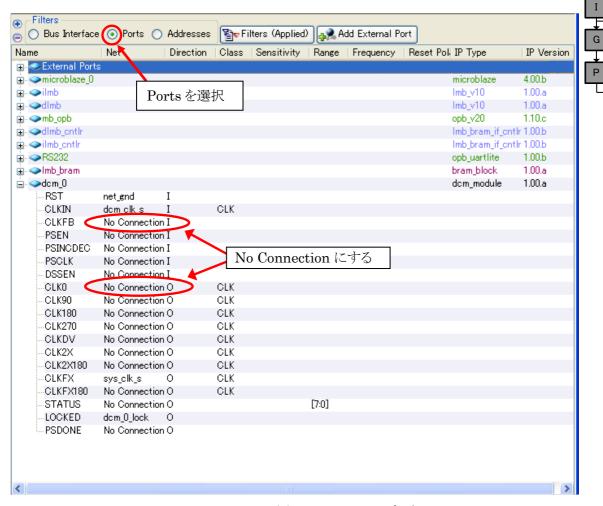

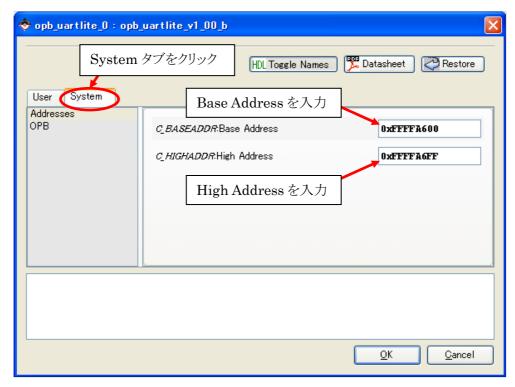

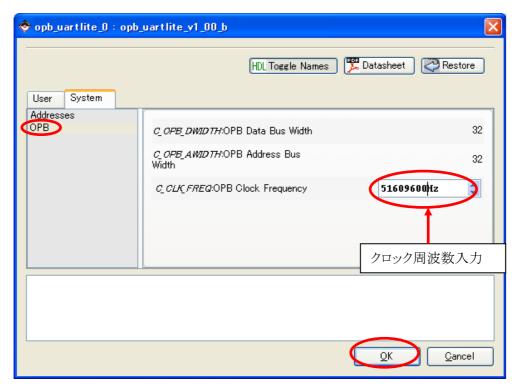

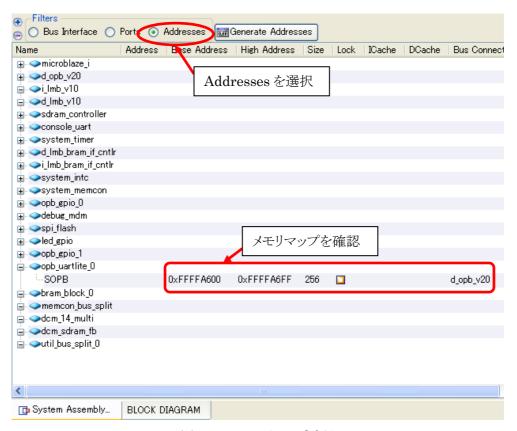

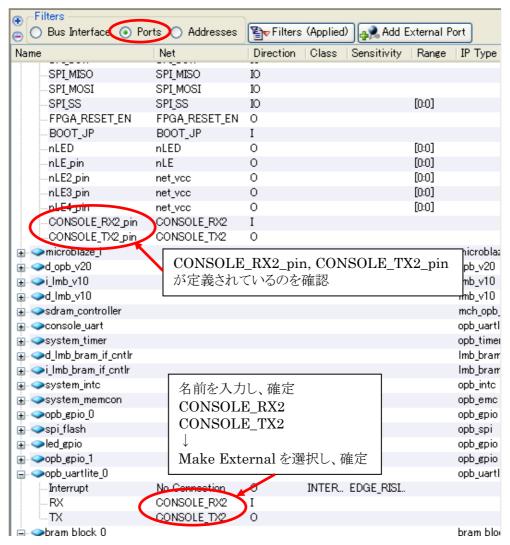

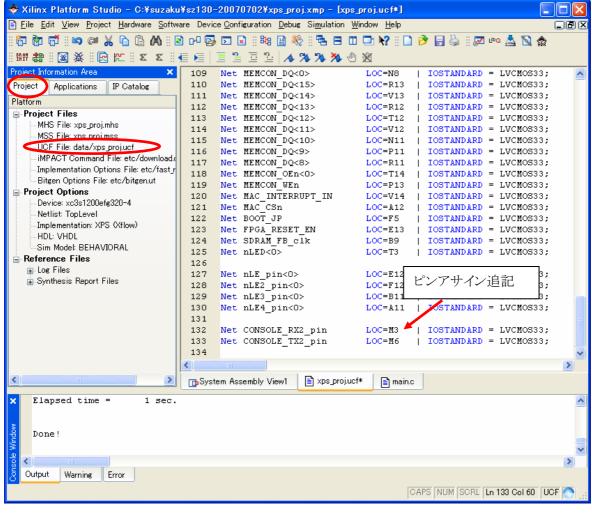

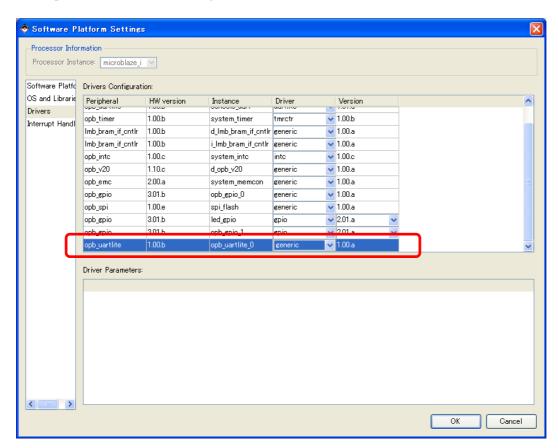

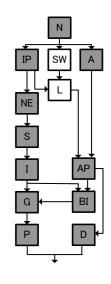

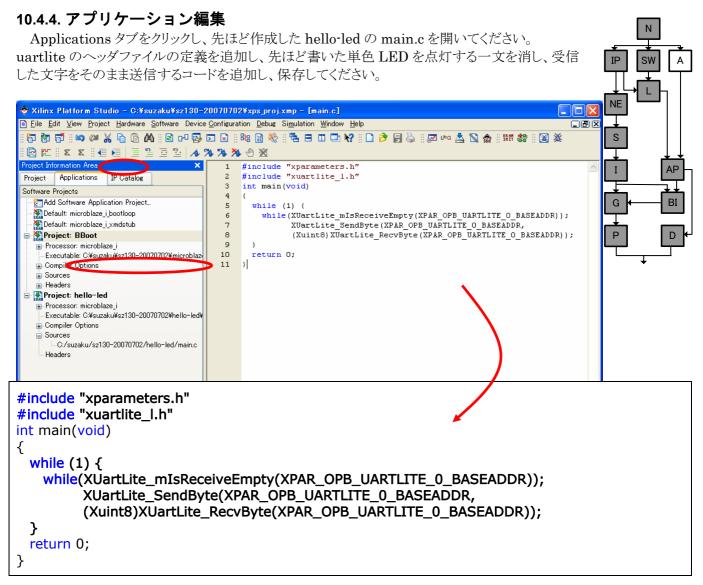

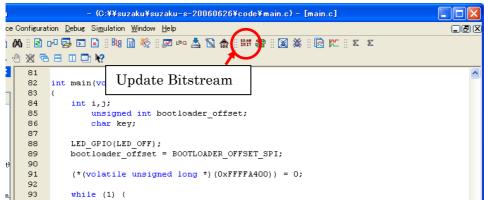

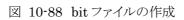

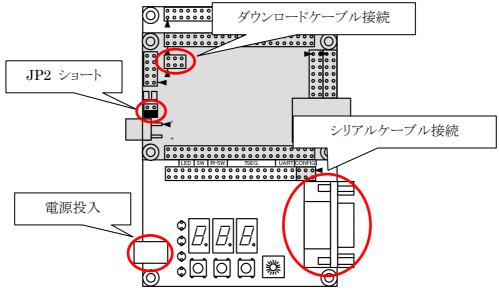

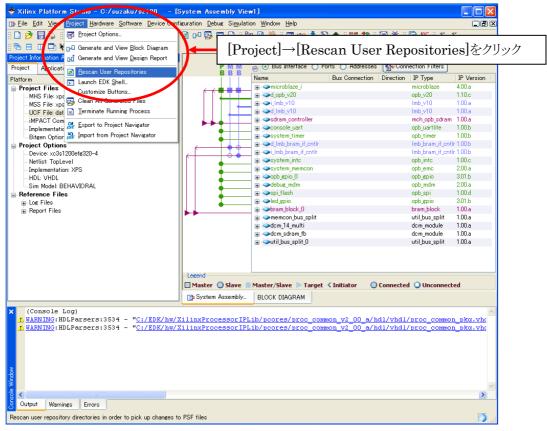

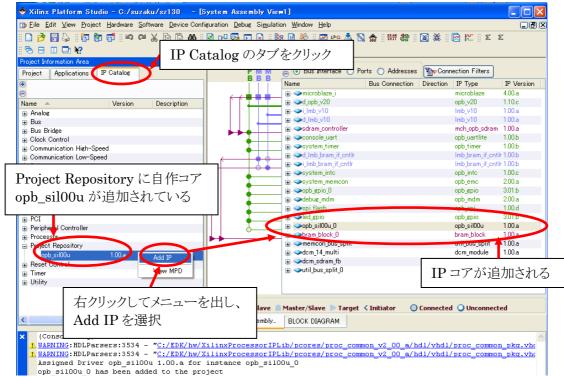

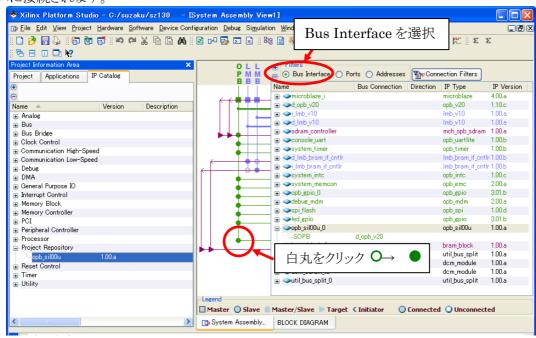

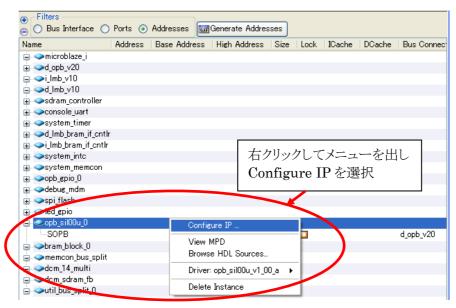

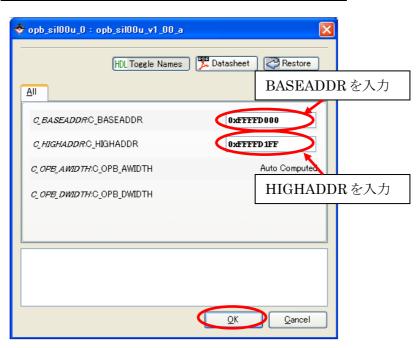

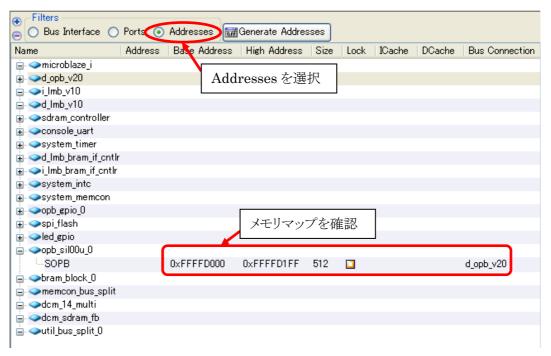

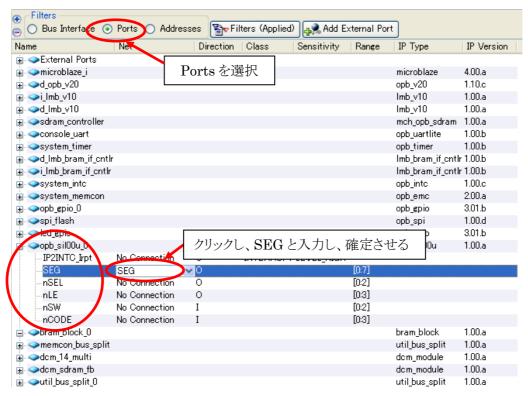

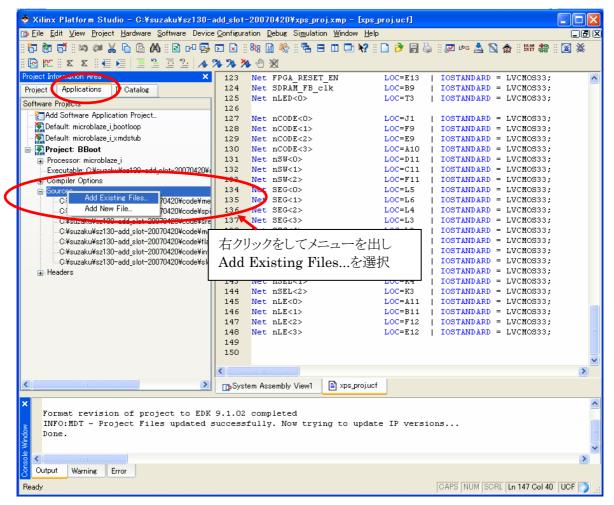

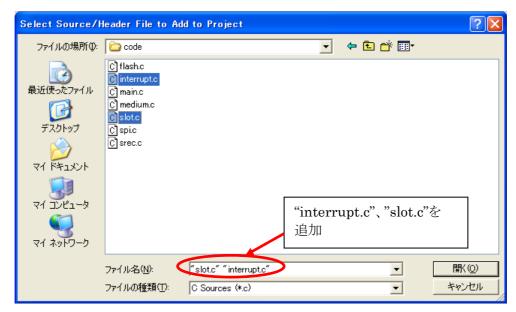

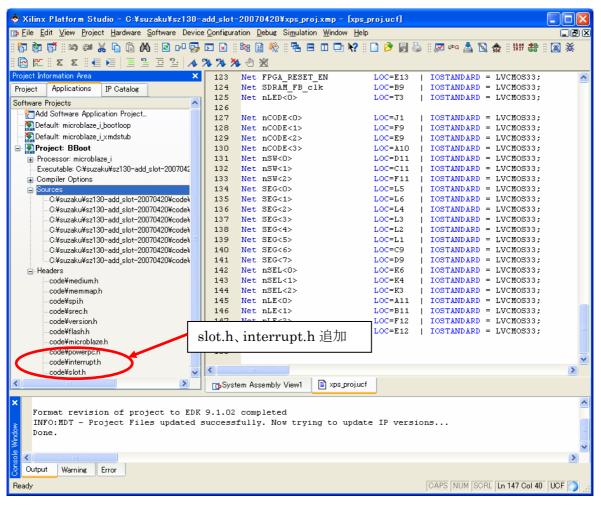

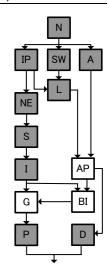

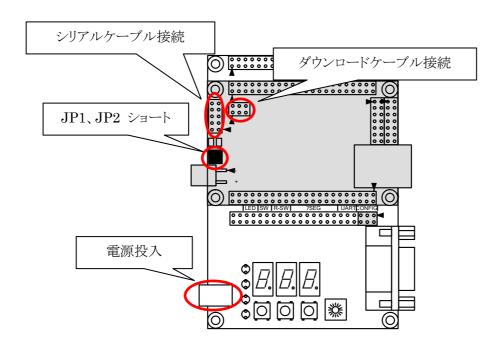

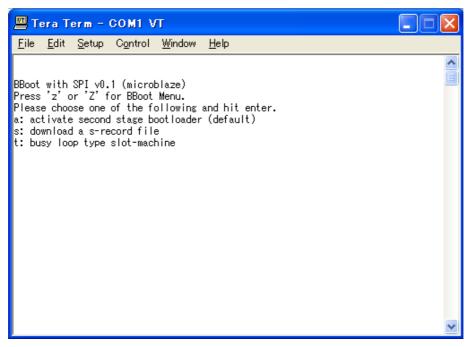

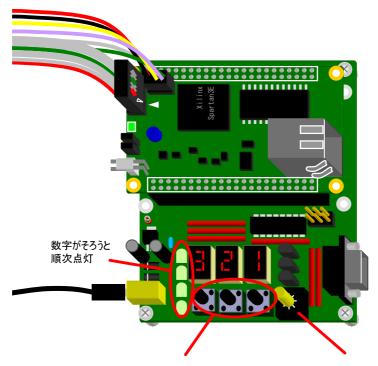

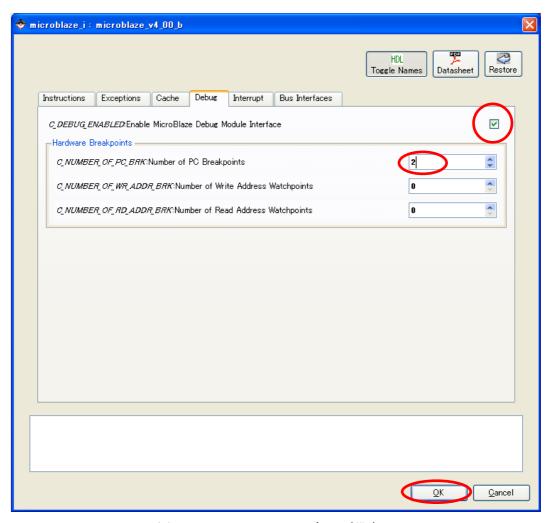

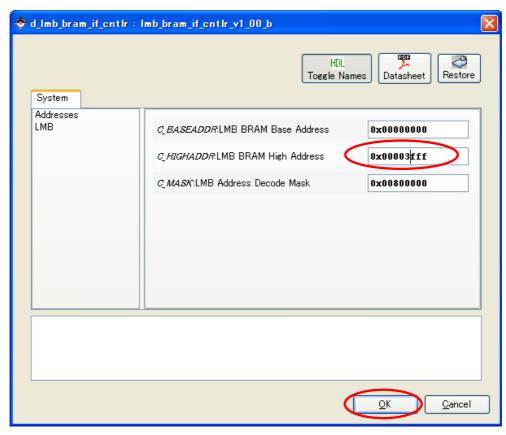

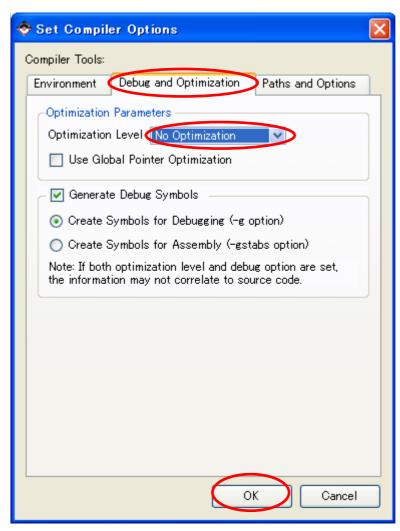

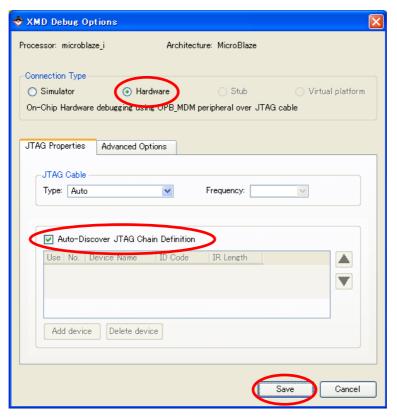

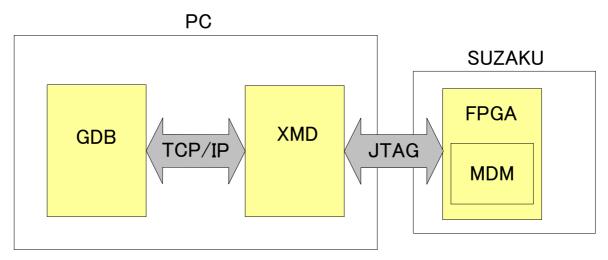

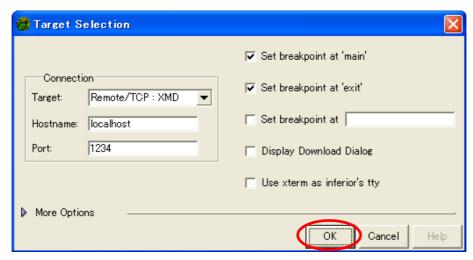

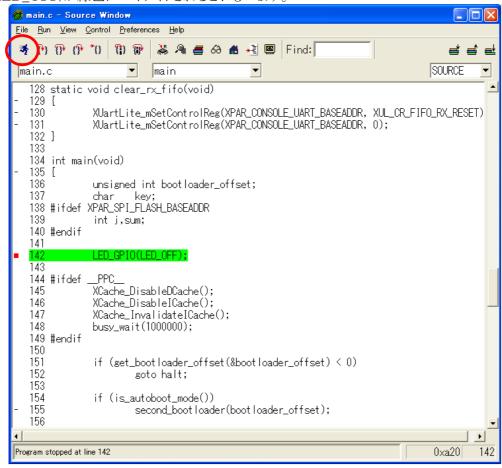

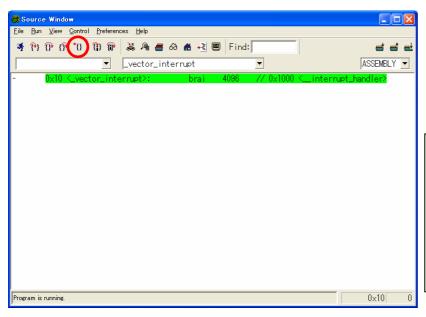

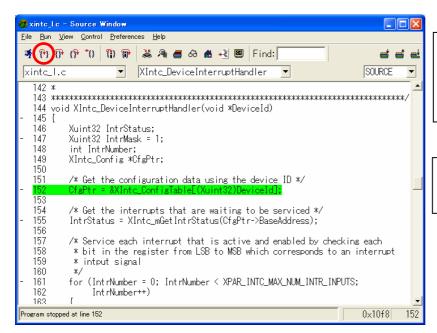

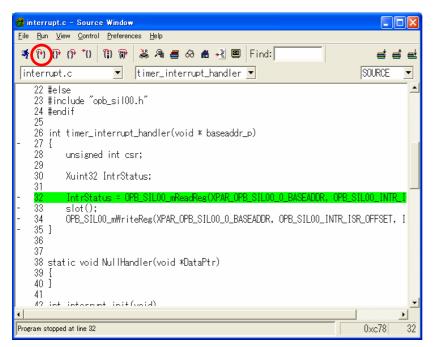

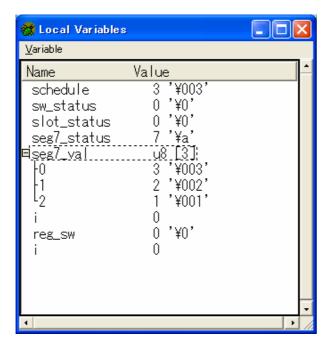

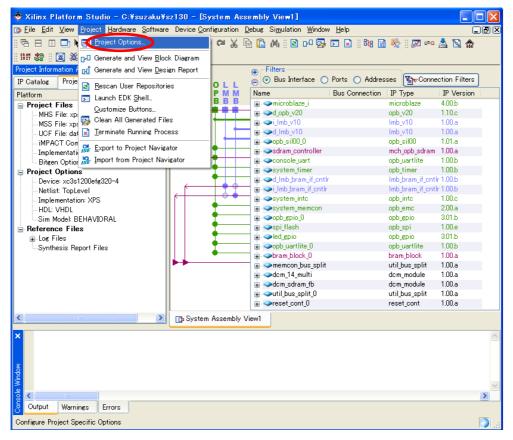

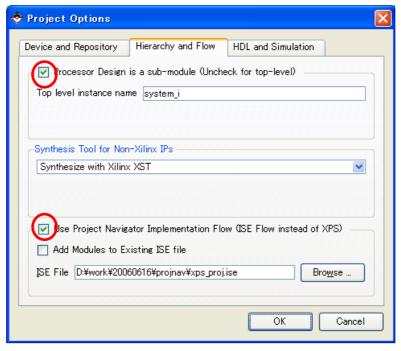

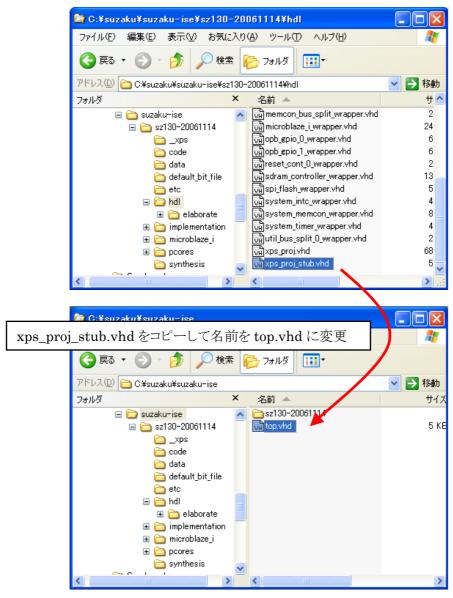

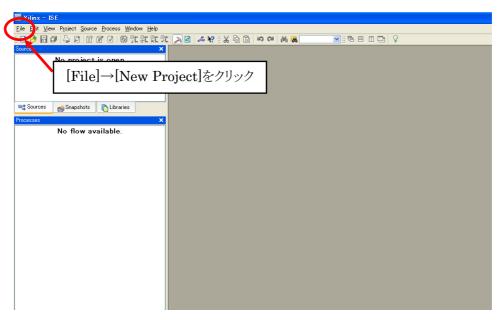

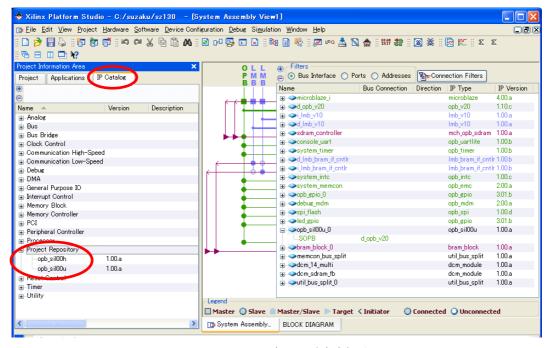

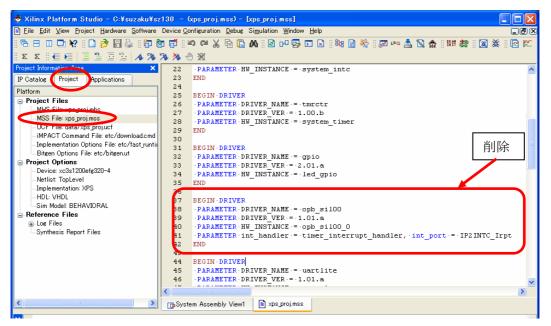

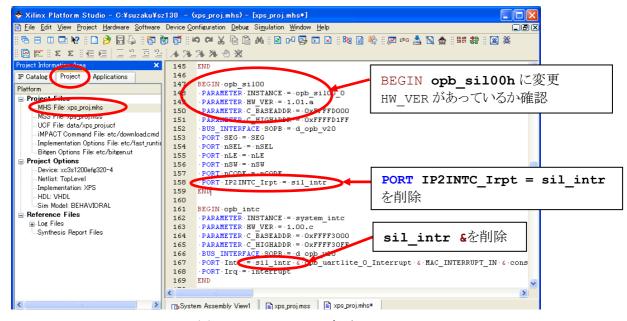

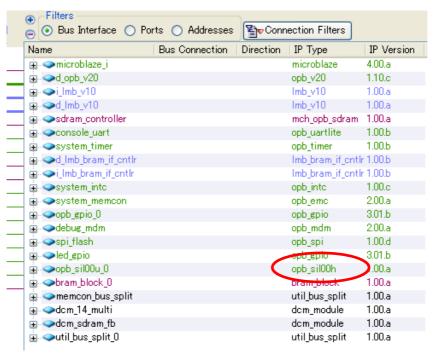

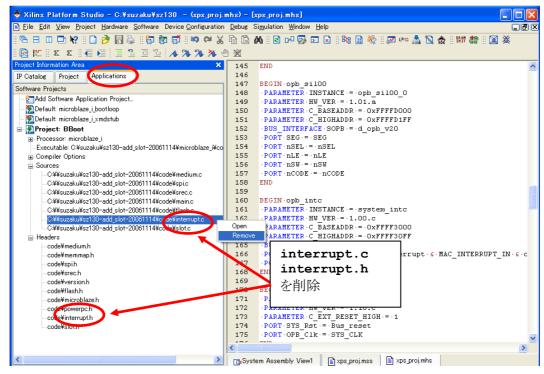

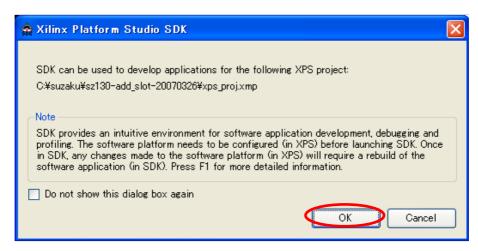

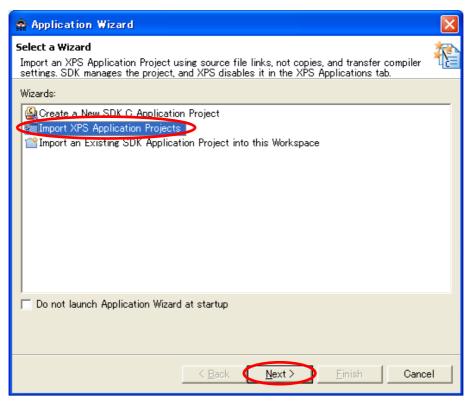

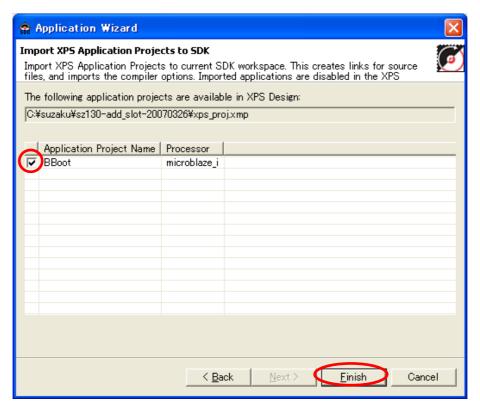

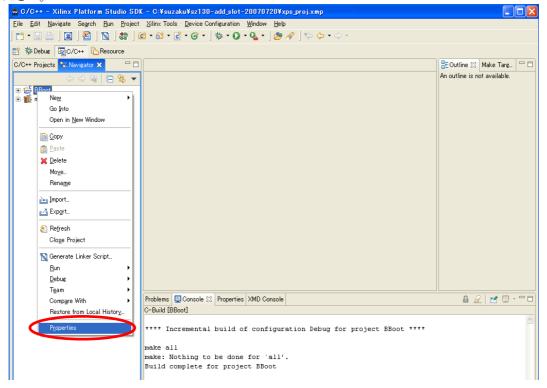

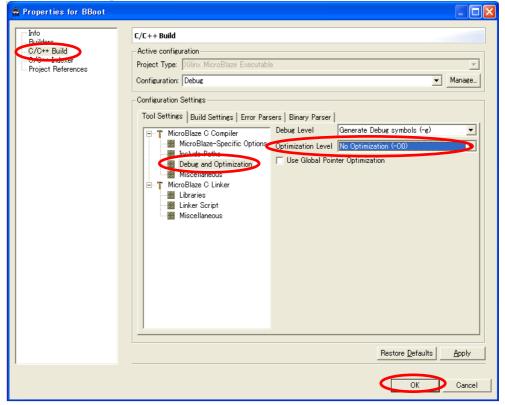

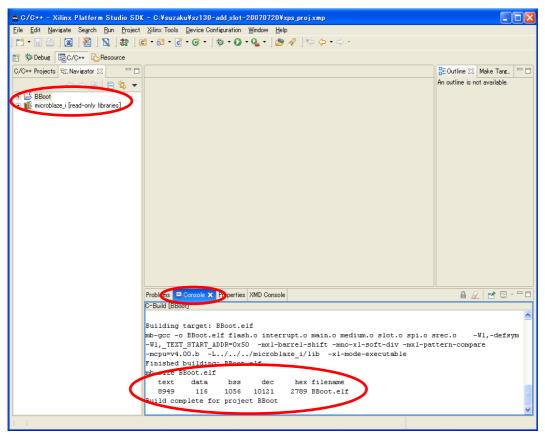

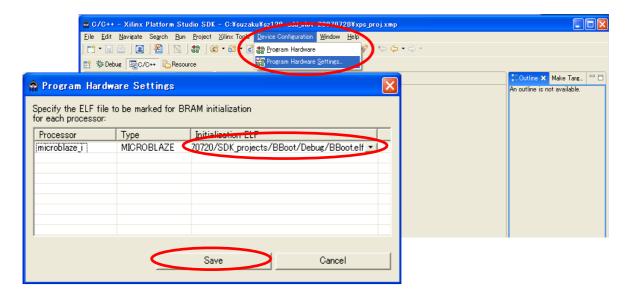

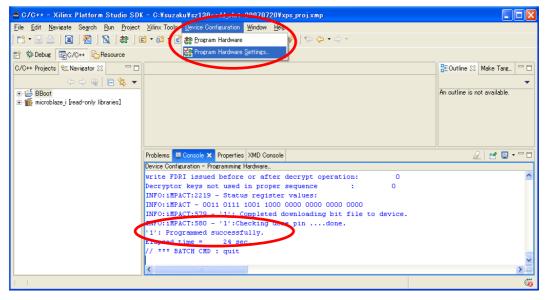

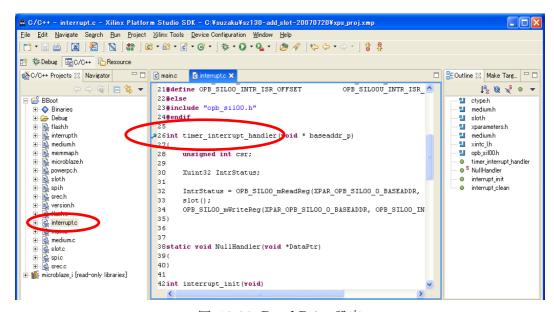

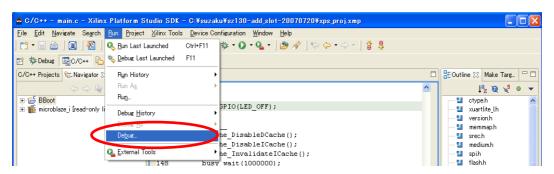

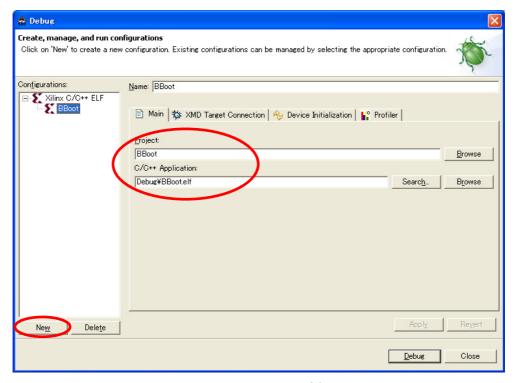

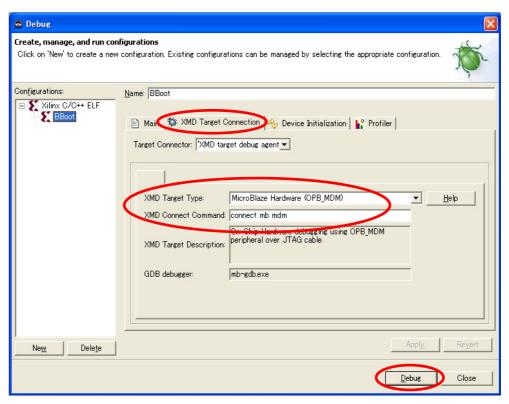

| 31 | nCODE0 | I   | ロータリコードスイッチ 20  | C10            | A10   | J13   | U9    |