## NS9750B-A1

Errata

90000738, Rev E

Release date: January 2006

Use in conjunction with: NS9750B-A1 Hardware Reference, Rev. A

Part number: 90000737\_A Released: August 2005

**Technical Support:**

Phone: 1.877.912.3444

Web: techpubs@digi.com

- UART gap timer

- UART CTS-related transmit data errors

- USB OVR and USB PWR

- PCI arbiter senses false request

- Ethernet receive data FIFO overflow (Ethernet receiver stall)

- 1284 nibble ID negotiation

- Linked Ethernet TX buffer descriptors do not work with late collisions

www.digi.com

1

## **UART** gap timer

The start bit of a new character may not be detected when the character or buffer gap timer expires. Framing, parity, or data corruption occur when a start bit is missed.

Software workaround: Three conditions have been identified for this erratum:

- Applications with a steady stream of receive data are not affected if the buffer gap timer is disabled.

- Applications where the gap between characters is fixed and the character gap timer period is configured to be less than the fixed period. The buffer gap timer must be disabled.

- Applications that have higher-level protocol error detection and recovery such as PPP can use both the buffer and character gap timers.

### Hardware workaround:

**Note:** The hardware workaround requires that you have installed the appropriate software patch found in the NETOS SW Toolkit (on the Web).

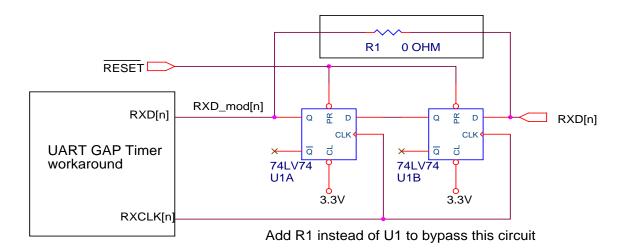

A hardware workaround eliminates the possibility of receiving a start bit when a character or buffer gap timer is expiring. The workaround drives the baud clock off-chip and synchronizes the incoming data with this clock. As a result, the buffer and character gap timers and the next start bit have a fixed and known relationship with each other.

#### Limitations:

- The TMODE bit in the Bit-rate register must be cleared.

- Baud rates are limited to those available in x16 mode

- Baud rates with a divisor of 0 are not possible for all CPU frequencies. This translates to a maximum baud rate of 460k in x16 mode.

- Baud rates with a divisor of 1 are not possible for CPU frequencies below 147MHz. This translates to a baud rate of 230k in x16 mode.

- The buffer and character gaps must be an even multiple of the sample clock period. For a 96000bps UART in x16 UART mode, the equation is:

- Timer increment =  $((1/9600) / 16) \times 2 = 13.020$ us

- One GPIO per UART is required to output the baud clock. The baud clock can be output on the RI pin on each UART. This function is controlled by the RXEXT bit (27) in each Serial Bit-rate register.

If multiple UARTs are running at the same baud rate, one baud clock can be used for the multiple UARTs.

### **UART CTS-related transmit data errors**

A problem occurs with the CTS flow control signal is de-asserted during the BCLK that begins processing a new character. This problem causes the previous character to be resent instead of getting the next character from the transmit FIFO.

#### Software workarounds:

- Modify these bits in Serial Channel Control register A:

- Set the CTSTX bit (bit 23) to 0 to disable hardware-controlled CTSTX.

- Set the ERXCTS bit (bit 4) to enable the software CTS signal change interrupt.

- Update the serial transmit ISR to handle the CTS signal change.

- The maximum bytes in each DMA buffer descriptor is limited to 16 bytes.

- The maximum skid rate can be up to 16 characters.

- The serial monitor thread is changed to handle the missing CTS interrupt.

See the appropriate (6.0 or 6.3) NET+OS SW toolkit (on the Web) for the required software workarounds.

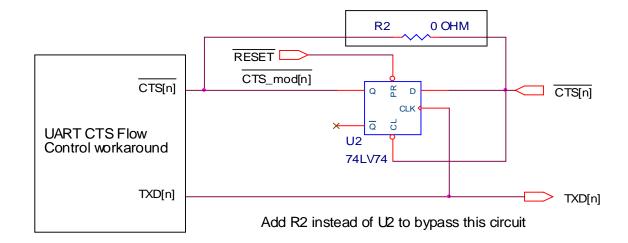

Hardware workaround: For each UART, externally clock the CTS signal with the Txd\_n signal to guarantee that CTS will not be seen de-asserting at the start of a character.

#### USB OVR and USB PWR

The USB OVR (over current) input on gpio[16] is not shown in the GPIO MUX pinout tables. The polarity of this signal cannot be changed. It is true high, normally requiring an external inverter and noise filter to prevent false indications of over current.

This table shows the corrections to GPIO[16] in the pinout table:

| Signal   | Mode         | Description                                |  |

|----------|--------------|--------------------------------------------|--|

| gpio[16] | 00           | Reserved output                            |  |

|          | 01           | 1284 nFault (peripheral driver, duplicate) |  |

|          | 02           | Timer 11 (duplicate), USB OVR              |  |

|          | 03 (default) | GPIO 16                                    |  |

Updates are required to the BSP to change gpio[16] from mode 00 to mode 02. Timer 11 is disabled, allowing USB OVR to be recognized by the USP IP. Even though Timer 11 is disabled, the Timer clock select field must be set to 111-External pulse event to set GPIO[16] to an input.

If you are using USB Host, GPIO[16] *must be reserved* for the USB OVR function.

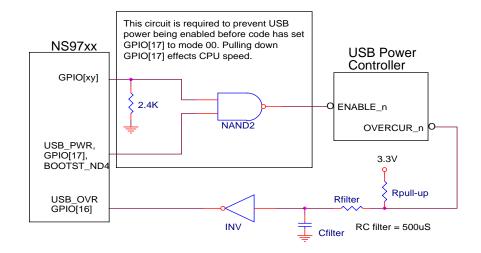

The USB PWR (power) control output requires additional external logic and GPIO to prevent USB power from being enabled from the time power is valid until the code has set the USB registers and selected gpio[17] to mode 00. The polarity of USB PWR is true high. Pulling down GPIO[17] to disable the USB power control changes the CPU bus speed because this pin is also bootstrap — ND4.

Designs that add the additional GPIO to prevent USB power-on during startup would require the BSP, as a final step, to set this GPIO to output a 1.

This figure shows a recommended logic workaround:

# PCI arbiter senses false request

For complete information and workarounds for this issue, see the related application note at http://www.netsilicon.com/support/appnotes.jsp

### Ethernet receive data FIFO overflow (Ethernet receiver stall)

The Ethernet receiver intermittently locks up in 100 Mbps half-duplex applications due to an overflow in the RX data FIFO.

Workaround: Reset the RX Ethernet logic when an RX\_OVFL\_DATA interrupt is generated. Go to http://www.netsilicon.com/support/appnotes.jsp to read the related

Application note for instructions for doing this.

# 1284 nibble ID negotiation problem

The NS9750B-A1 should set the Xflag (Select) line low at event #6 (see the IEEE 1284 standards specification). Instead, this signal is being driven high. The host uses this signal to determine whether the requested mode is supported. Therefore, the host incorrectly concludes that the NS9775 does not support nibble ID mode.

Workaround: None.

# Linked Ethernet TX buffer descriptors don't work with late collisions

If the Ethernet transmitter locks up when a late collision occurs while transmitting an Ethernet package consisting of multiple linked buffer descriptors, one of these situations occurs:

- The WRAP bit in the last entry of the embedded TXBD RAM is cleared.

- The WRAP bit is set in both the first and last entries in the TXBD RAM.

Workaround: Software keeps a shadow copy of the TXBD RAM flags in main memory, and updates the copy only when the CPU accesses the TXBD RAM. When the CPU receives an Ethernet TX ERROR interrupt of any kind (that is, the TXERR bit is set in the Ethernet Interrupt Status register), which includes a late collision, the CPU takes this action:

- Reads the TX Error Buffer Descriptor Pointer register (TXERBD), which, in the case of the logic error, points to the location that has the bad WRAP bit.

- Copies the flags from the shadow TXBD RAM to the real TXBD RAM starting at the location pointed to by the TXERBD and ending at the first shadow location that has the LAST bit set, indicating the last buffer descriptor for the packet. This corrects the WRAP bit errors.

© Digi International Inc. 2005-2006 All rights reserved.

Digi and Digi International are trademarks or registered trademarks of Digi International Inc. in the United States and other countries worldwide. NetSilicon, NET+Works, and NET+OS are trademarks of NetSilicon, Inc. ARM is a registered trademark of ARM limited. NET+ARM is a trademark of ARM limited and is exclusively sublicensed to NetSilicon. All other trademarks are the property of their respective owners.

Information in this manual is subject to change without notice and does not represent a commitment on the part of Digi International.

Digi provides this document "as is," without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of, fitness or merchantability for a particular purpose. Digi may make improvements and/or changes in this manual or in the product(s) and/or the program(s) described in this manual at any time.

This product could include technical inaccuracies or typographical errors. Changes are made periodically to the information herein; these changes may be incorporated in new editions of the publication.

Digi International 11001 Bren Road East Minnetonka, MN 55343 U.S.A. United States: +1 877 912-3444 Other locations: +1 952 912-3444

Fax: +1 952 912-4960 www.digi.com/support

www.digi.com

Online problem reporting: www.digi.com/support/eservice/eservicelogin.jsp